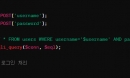

차세대 그래픽 메모리나 모바일 메모리 등을 겨냥한 초고속 DRAM 기술의 개발 성과가 최첨단 반도체 기술 국제 회의 "ISSCC 2016"에 공개됐다. DRAM 최고 대형 벤더사인 삼성전자와 DRAM 대형 벤더인 SK 하이닉스가 각각 2건씩 개발 칩을 발표했다. 삼성 일렉트로닉스는 GDDR5 메모리와 HBM2, SK 하이닉스는 HBM2와 Wide-IO2 메모리를 각각 선보였다.

싱글 엔드 핀당 9Gbit/sec의 초고속 GDDR5 메모리

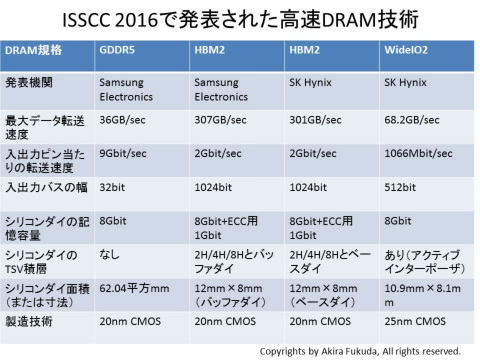

삼성전자는 입출력 핀당 데이터 전송 속도가 9Gbit/sec으로 매우 높은 GDDR5 DRAM을 개발하고 기술 개요를 발표했다(강연 번호 18.1). "GDDR5"는 그래픽용 고속 메모리 규격 사양인 "GDDR(Graphics Double Data Rate)"의 제 5세대를 의미한다. GDDR 시리즈 규격 사양은 업계 단체 JEDEC이 책정을 계속했다. GDDR5 DRAM 양산 출하는 2008년에 시작됐고 그래픽용 DRAM으로서는 꽤 긴 역사를 갖고 있다.

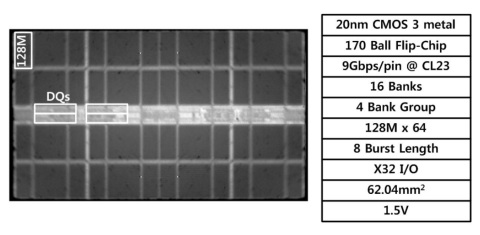

9Gbit/sec라는 데이터 전송 속도는 싱글 엔드 출력의 메모리 반도체에서는 최고 속도의 가능성이 높다. 삼성은 2011년 ISSCC(ISSCC 2011)에서 입출력 핀당 데이터 전송 속도가 7Gbit/sec으로 높은 GDDR5 DRAM을 제작 발표하고 있다.(논문 번호 28.6) 이 속도도 당시 반도체 메모리의 싱글 엔드 출력으로 역대 최고 속도라 보이고 있었는데 5년만에 최고 속도 기록을 새로 쓴 것이다.

5년전 ISSCC에서 삼성이 발표한 GDDR5 DRAM은 기억 용량이 2Gbit, 입출력 버스폭이 32bit, 데이터 전송 속도가 28GB/sec, 실리콘 다이 면적이 80.6평방mm, 제조 기술이 40nm CMOS. 이번 ISSCC에서 삼성이 발표한 GDDR5 DRAM은 기억 용량이 8Gbit, 입출력 버스폭이 32bit, 데이터 전송 속도가 36GB/sec, 실리콘 다이 면적이 62.04평방mm, 제조 기술이 20nm CMOS로 나타났다. 기억 용량은 4배로 늘고 데이터 전송 속도는 약 1.3배 향상, 제조 기술은 50% 미세화되고 기억 밀도는 5.2배로 늘었다.

300GB/sec의 초 광대역을 실증한 HBM2 DRAM

GDDR5 DRAM의 고속화는 교착 상태를 맞고 있다. 삼성은 이번 ISSCC에서 빠른 성능을 더욱 향상시켰다고해도 매우 고도의 기술을 여러가지 구사하고, 오히려 고속화가 매우 어려워지고 있는 상황을 알리게 된 감이 있다.

GDDR5 DRAM을 대체하는 것을 목적으로 업계 단체 JEDEC이 기술 사양을 책정한 고속 메모리가 HBM(High Bandwidth Memory)이다. ISSCC 2016에서는 HBM의 제 2세대("HBM Gen2" 혹은 "HBM2"라 지칭)에 해당하는 DRAM의 개발 성과를 삼성전자(강연 번호 18.2)와 SK 하이닉스(강연 번호 18.3)가 각각 발표했다.

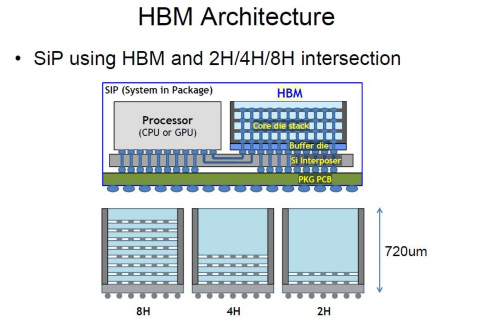

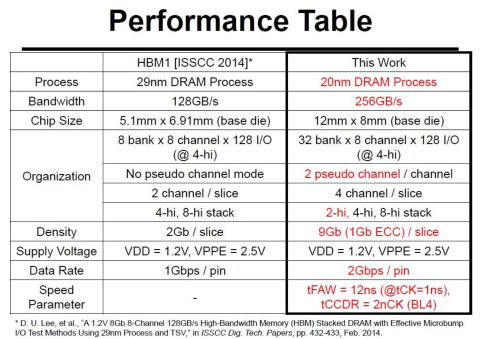

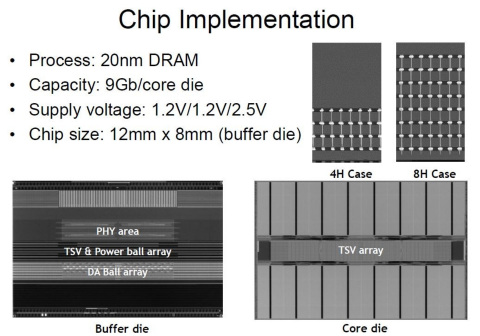

HBM은 2장 또는 4장, 8장의 DRAM 실리콘 다이를 TSV(실리콘 관통 전극)기술로 적층 하는 8채널 ×128bit(128핀)의 넓은 입출력 버스를 갖춤으로써 데이터 전송 속도를 향상시킨다. 1세대 "HBM Gen1(HBM1)"은 핀당 데이터 전송 속도는 1.0Gbit/sec이다. GDDR5 와 DDR4 등의 DDR 시스템 메모리에 비해 핀당 데이터 전송 속도를 낮춤으로써 출력 드라이버의 설계와 제조를 쉽게 받아 실리콘 다이의 수율 향상과 제조 원가의 절감을 노리고 있다. 그래도 전체적으로는 128GB/sec과 DDR 시스템 메모리를 훨씬 뛰어넘는 높은 데이터 전송 속도를 갖는다.

HBM의 2세대 "HBM2"는 입출력 핀당 데이터 전송 속도를 2배인 2Gbit/sec으로 높임으로써 전체 데이터 전송 속도를 256GB/sec으로 2배 향상시킨 것이 주요 변경점이다. 또 풀 대역에 대한 사양이 개량됐다. 1세대 "HBM1"에서는 DRAM 실리콘 다이를 4장 또는 8장으로 적층해 처음으로 풀 대역(128GB/sec)를 낼 수 있게 됐다. 2장 적층에서는 풀 대역의 절반(64GB/sec)밖에 나오지 않았지만 HBM2는 DRAM 다이의 2장 적층으로도 풀 대역(256GB/sec)이 나올 수 있도록 아키텍처를 개량했다.구체적으로는 실리콘 다이당 입출력 버스폭을 HBM1의 256bit로부터 HBM2는 최대 512bit로 변경했다.

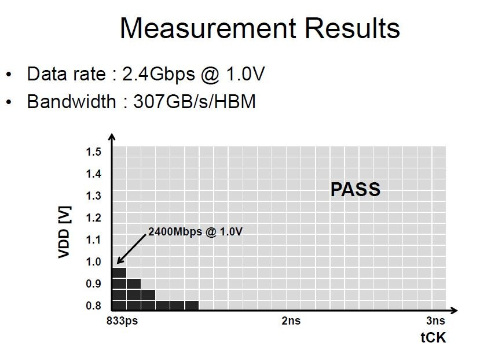

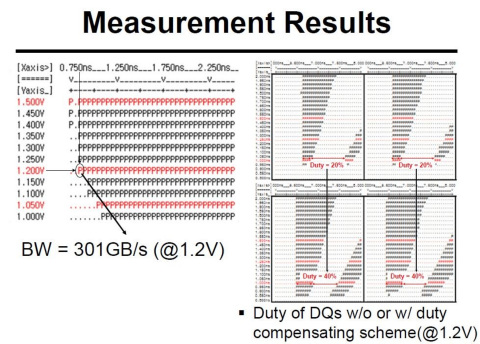

ISSCC에서 발표된 HBM2의 실제 성능은 규격 사양인 256GB/sec을 넘어섰다. 삼성의 시제품이 307GB/sec, SK 하이닉스의 시제품이 301GB/sec을 달성했다. 양사 모두 완성도 높은 메모리를 제조하는 것으로 나타났다.

고속성과 저전력을 양립시키는 Wide-IO2 메모리

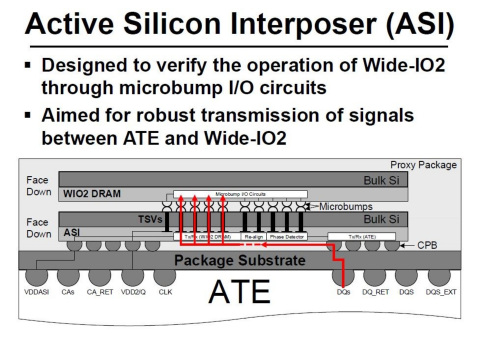

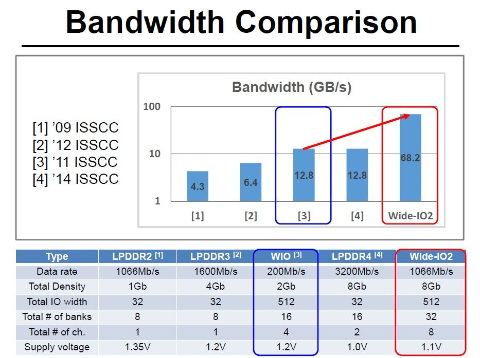

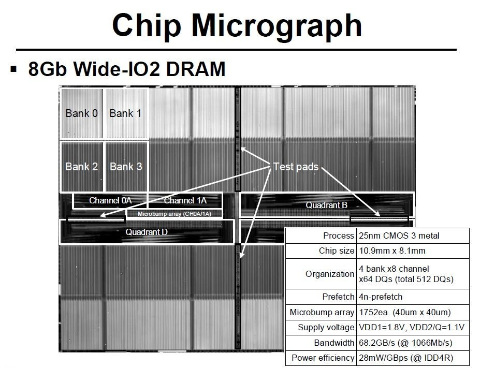

고속성과 낮은 소비 전력을 양립시키는 것으로 전력 효율을 추구한 기술 사양이 "Wide-IO2" 메모리다. DDR 시스템 메모리에 비해 데이터 전송 속도를 높이고 전송 속도당 소비 전력은 낮춘 "Wide-IO2"의 기술 사양도 업계 단체 JEDEC이 책정했다. ISSCC 2016에서는 SK 하이닉스가 Wide-IO2 규격에 준거한 DRAM의 테스트 결과를 발표했다.(강연 번호 18.4)

Wide-IO2 메모리는 입출력 버스의 폭을 512bit(512핀)로 넓게 확보하여 고속 데이터 전송을 실행하고 핀당 데이터 전송 속도를 낮춤으로써 소비 전력을 절감하고 있다.

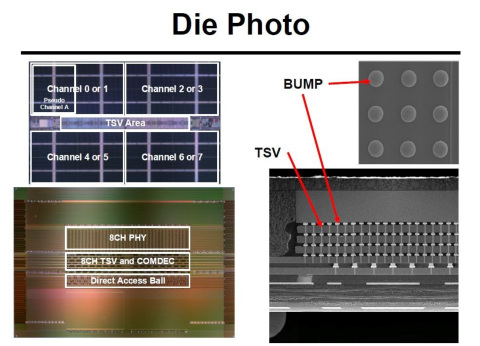

메모리의 기본 구성은 2장의 실리콘 다이 SiP(시스템 인 패키지)다. 1장은 DRAM 다이, 다른 1장은 인터포저. 인터포저에는 제어 논리 회로와 TSV 전극을 만들고 있다. 패키지 기판 위에 인터포저가 페이스 다운으로 연결되고 인터포저 뒤에 DRAM 다이가 페이스 다운으로 연결된다.

개발한 Wide-IO2 메모리의 성능은 입출력 핀당 데이터 전송 속도가 1,066Mbit/sec, 전체 데이터 전송 속도는 68.2GB/sec이다. LPDDR4 DRAM 보다 대역이 넓다.

출처 - http://pc.watch.impress.co.jp/docs/news/event/20160212_743223.html

가상현실 시작! 오큘러스 레디PC ...

가상현실 시작! 오큘러스 레디PC ...

애플실적 발표 - 정점에 도달한 ...

애플실적 발표 - 정점에 도달한 ...