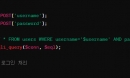

새로운 프로세스 기술의 시작, 인텔에게 조차 프로세스의 이행은 살얼음판을 걷는 듯한 느낌이라고 한 업계 관계자는 밝혔다. 1세대마다 새로운 프로세스의 기술적 어려움은 높아져 2년마다 이행 속도를 지키는 것은 매우 힘들어지고 있다. 특히 처음으로 FinFET 3D 트랜지스터(인텔의 명칭은 TriGate)를 도입한 22나노 과정의 첫 시작기는 사내에서도 꾀 안달을 해 결과적으로 22나노 프로세스는 제품 출하를 볼때 대성공으로 이번의 제품 수율도 높을 것으로 보이고 있다.

22나노 과정이 성공했던 것은 인텔의 인사를 봐도 알수 있다. 인텔이 새로운 CEO로 선택한 것은 제조를 담당해 온 크르자니크였다. 제조 분야의 인물을 탑으로 한 인사는 인텔의 제조가 FinFET 시대에도 잘 될 것이라는 증거다. 또 뒤집어 보면 그 만큼 반도체 제조가 어렵고 중요하다는 것을 나타내고 있다.

인텔은 이번 개발 컨퍼런스 "Intel Developer Forum"(IDF)에서 다음 14나노 프로세스가 잘 진행되고 있음을 어필할 필요가 있었다. FinFET으로 2세대째인 14나노 프로세스는 인텔이 타사를 따돌리는 관건.

파운드리 기업 TSMC와 GLOBALFOUNDRIES는 현재 제품을 출하 하고 있는 최첨단 프로세스는 평면 2D 트랜지스터의 28나노 프로세스로 그 다음이 20나노지만 잘 진행되고 있지 않고 20나노 또한 핀펫 트랜지스터가 아니다.

파운드리 프로세스에 FinFET이 도입되는 것은 1년 후인 16/14나노 프로세스다. 16/14나노 프로세스는 백엔드는 20나노 세대와 공통화를 추진하고, 트랜지스터를 FinFET으로 교체하는 것이 된다. 인텔의 프로세스는 성능 튜닝에 특화 되어 있어 파운드리 프로세스와 비교하면 게이트 피치는 컸다. 그 때문에 파운드리 측은 20나노의 백엔드를 써도 16/14nm 프로세스에서 인텔의 14나노와 동등하다고 하고 있다. 즉, 지금은 인텔이 프로세스 기술에서 독주 상태지만 14나노 세대에서는 타사가 필사적으로 추격하고 있기 때문에 14나노를 재빨리 만들어 우위를 지속할 필요가 있다.

인텔은 이번 IDF에서 14나노 세대의 PC용 CPU 브로드웰의 라이브 시연을 보였다. 14나노 공정의 시작이 순조로워 2014년에 출하가 가능하다고 나타내는 의미가 있다. 그리고 인텔은 14나노 프로세스기 때문에 성능/효율을 더욱 향상시킬 수 있는 점을 나타내 보였다.

IDF에서 우선 CEO 크르자니크가 브로드웰을 소개했다. 그것도 브로드웰을 탑재한 울트라북에서 윈도우8이 동작하고 있는 모습을 공개했다. 브로드웰이 완전히 동작하는 상태로 시스템에 탑재할 수 있는 단계라는 사실을 입증했다.

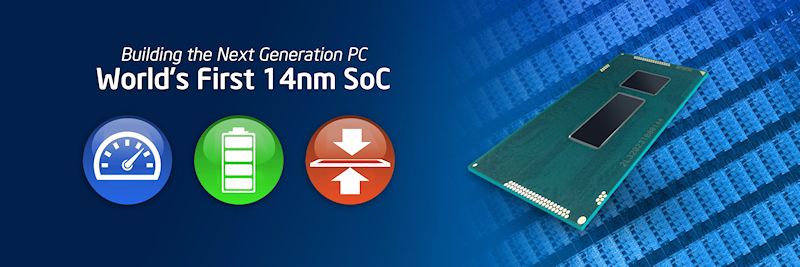

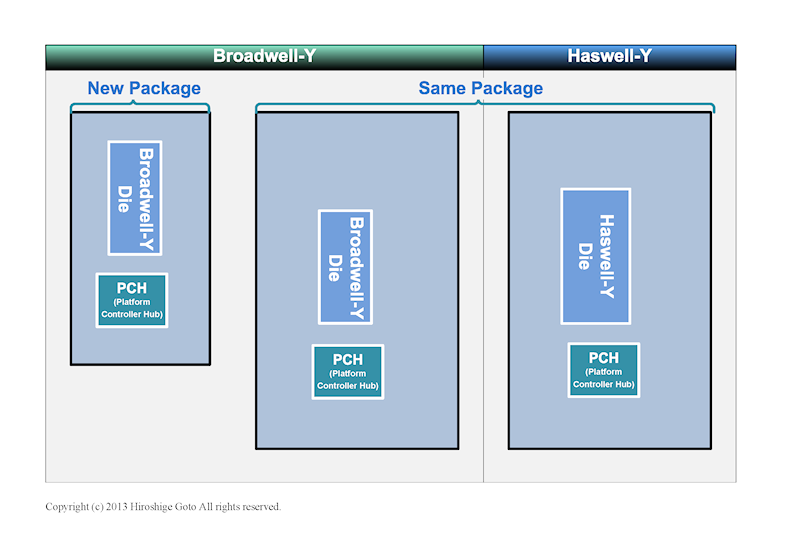

크르자니크는 태블릿 스타일까지 커버하는 저전력 Y프로세서 패밀리의 브로드웰-Y에 보다 소형 패키지 도입을 발표하며 브로드웰-Y에 하스웰-Y와 핀 호환이 되는 240×400mm 패키지로 제공할 뿐만 아니라 공간 절약 패키지(165×300mm)도 제공한다.

실제로 현재의 하스웰-Y의 패키지와 브로드웰-Y의 새 패키지가 나타났다. 이에 따르면 패키지와 다이의 배치는 아래와 같다. CPU의 다이 아래 부분은 I/O를 정리한 PCH(Platform Controller Hub)칩의 다이다. 2칩을 정리한 MCM(Multi-Chip Module) 형태로 인텔은 SoC(System on a Chip)라 부르고 있다.

또 인텔의 스코겐이 브로드웰-Y 프로세서를 설명, 브로드웰-Y는 하스웰-Y 성능대비 약 30%의 소비 전력을 낮은 점을 CINEBENCH의 시연으로 입증했다. 이 데모에서 아키텍쳐가 하스웰과 크게 다르지 않은 브로드웰이 14나노 프로세스의 이행에 따라 액티브시 전력 절감을 달성할 수 있음을 나타내 보였다.

스코겐은 이 시연은 아직 브로드웰-Y의 성능 튜닝을 하기 전의 것이라고 설명하며 앞으로 수개월에 걸쳐 튜닝을 하고 더욱 성능/전력이 향상할 것이라고 시사했다.

이번 IDF에서 브로드웰-Y에 대해 인텔이 강조한 것은 팬 리스 시스템을 보다 일반화하는 것으로 냉각에 가장 문제가 되는 것은 단위 면적당 전력 소비 지표인 전력 밀도다. 팬 리스 시스템을 쉽게 하기 위해서는 일반적으로 전력 밀도를 떨어뜨려야 한다. 그러나 역설적으로 프로세스를 미세화하고 다이를 작게 할수록 전력 밀도는 높아진다.

이론상 트랜지스터가 1세대 미세화되면 게이트 자체가 소형화되어 용량은 약 70%감소한다. 그러나 게이트 면적은 약 50%로 감소하기 때문에 같은 전압에서 구동하는 전력 밀도가 상승해 버린다.

사실 스코겐이 제시한 하스웰-Y에 비해 브로드웰-Y의 전력이 70% 절감된다는 숫자는 거칠게 말하면 저항 감소분에 불과하다. 만약 FinFET화로 저항을 순조롭게 줄일 수 있게 된 것이라면 70%의 감소는 당연하다는 것이다. 과거의 CMOS 계수 법칙에서 보면 70%는 놀라운 숫자는 아니다.

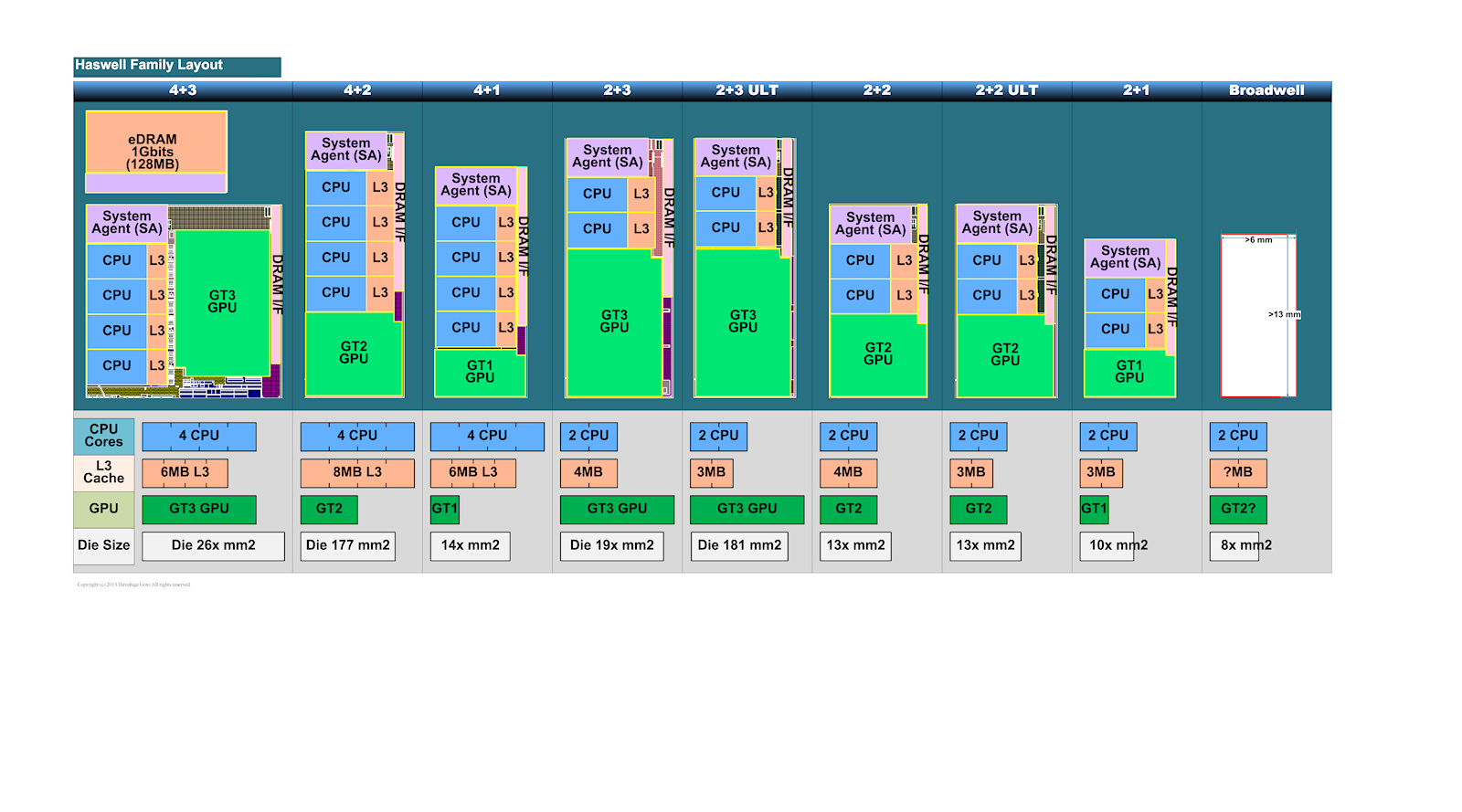

실제 브로드웰의 다이는 어떨까, IDF에서 공개된 Y프로세서의 다이는 단변이 6.2mm전후, 장변이 13.4mm전후로 다이 사이즈는 계산상 83kmm정도가 된다. 이를 하스웰 패밀리의 다이와 비교하면 아래와 같다. 우측이 브로드웰-Y.

브로드웰-Y의 다이를 하스웰-Y의 2+2구성의 다이와 비교하면 다이 면적의 축소율은 64%안팎이다. 이 축소율에 비해 전력 절감의 70%라는 비율은 아직 부족하다. 칩 전체의 TDP는 감소 시킬수 있지만 피크시의 전력 밀도는 어렵다. 따라서 전력 밀도는 떨어지지 않으므로 팬리스화는 설계 가이드 라인 등에 의해 시행해 나가게 된다.

브로드웰-Y에서 보이는 다이 축소와 전력 절감 비율의 불균형에 의한 전력 밀도의 상승은 현재의 CPU가 공통적으로 안고 있는 문제다. 전형적인 다크 실리콘 문제로 FinFET화도 이 문제에서 벗어날 수 없는 상황이 나타났다.

다크 실리콘 문제를 해결하는 방법은 여러가지 있지만 가장 쉬운 것은 CPU 다이에 CPU코어 외의 유닛을 더 탑재하는 것이다. CPU가 작동하고 있을 때 전력을 너무 소비하지 않는 유닛을 늘리면 다이 전체의 전력 밀도는 떨어진다. 다이상에서 열이 집중하는 핫 스팟은 되지만 어느 정도 분산시킬 수 있다.

미세화되는 브로드웰에서 상위의 더 큰 다이는 이 방향을 강화할 필요가 있다. 인텔 CPU의 경우는 SRAM과 GPU코어&비디오 프로세서가 가장 늘리기 쉬운 부분이다. CPU코어와 GPU코어가 각각 상대적으로 부하가 낮을 때 동작한다면 일정한 TDP(Thermal Design Power:열 설계 전력)와 일정한 전력 밀도의 범위 내에서 가동할 수 있기 때문이다.

이미 인텔 CPU도 GT3구성의 GPU코어를 올린 칩은 CPU코어의 면적보다 GPU&비디오 코어의 면적이 커지고 있다. 브로드웰 다음인 14나노 스카이 레이크에서도 같은 추세가 계속될 것이다.

(인텔 vs 나머지 모든 기업)

보도 - http://pc.watch.impress.co.jp/docs/column/kaigai/20130917_615603.html

에이수스와 에이서가 합병 논의중...

에이수스와 에이서가 합병 논의중...

네이버 라인 승승장구, 가입자 2...

네이버 라인 승승장구, 가입자 2...