STT-MRAM은 차세대 대용량 비휘발성 메모리의 유력 후보다. 원리적으로는 20nm 이하의 미세화가 가능하고 기억 용량당 실리콘 면적(제조 코스트)은 DRAM에 가까우며 읽기와 쓰기 속도도 DRAM에 가깝다. 데이터의 쓰기 횟수는 반영구적으로 데이터를 저장할 수 있을 정도인 10년 이상으로 길다.

이 원리적인 우위성이 그대로 현실이 된다면 STT-MRAM에 가장 가까운 이미지는 "비휘발성이 된 DRAM"이다. DRAM에 가까운 대용량과 낮은 비용을 양립할 수 있다면 DRAM의 일부를 대체할 수 있게 된다.

최근 STT-MRAM은 DRAM에 가까운 기가비트급의 대용량을 달성할 전망이 나온다. 그 최첨단을 달리는 것이 SK 하이닉스와 도시바의 STT-MRAM 공동 개발팀이다. 이 팀은 지난해(2016년) 12월에 미국 샌프란시스코에서 열린 국제 학회 "IEDM"에서 DRAM과 거의 동등한 4Gbit의 큰 기억 용량을 달성할 수 있는 STT-MRAM 기술을 개발했다고 공표했다.

그리고 올해(2017년) 2월 6일~8일(미국 시간) 미국 샌프란시스코에서 개최 중인 국제 학회 "ISSCC 2017"에서 SK 하이닉스와 도시바의 공동 개발팀은 4Gbit의 STT-MRAM 칩(실리콘 다이)를 발표했다.(강연 번호 23.5)

역대 최대의 기억 용량과 최고의 기억 밀도 달성

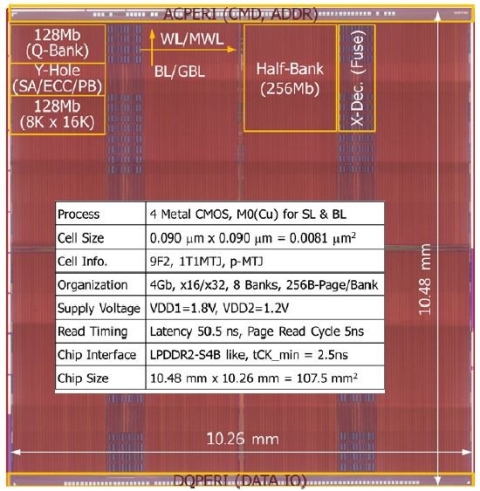

개발한 4Gbit 실리콘 다이의 외형 치수는 10.26×10.48mm로 거의 1cm. 기억 용량은 STT-MRAM으로 사상 최대다. 그리고 기억 용량당 실리콘 면적은 과거에 공표된 STT-MRAM의 값보다 훨씬 작다.

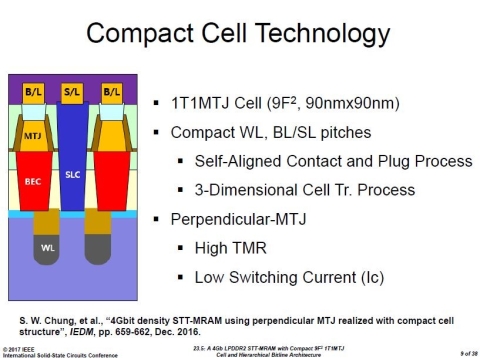

메모리 셀 치수는 90nm. 설계 치수의 2제곱(F2)으로 환산하면 9F2가 된다. 이것도 과거의 STT-MRAM 보다 훨씬 작다. 1개의 메모리 셀은 1개의 셀 셀렉트 트랜지스터와 1개의 자기 터널 접합(MTJ) 소자로 구성했다. MTJ 소자의 자기 기록 방식은 수직 기록 방식이다. 수직 자기 기록 방식의 MTJ 소자의 제조는 꽤 어렵지만 미세화에는 적당하다고 권한다.

설계 치수를 공표하고 있지 않지만 메모리 셀에 관한 치수 정보로부터 30nm라고 추정했다. 제조 기술은 4층 금속 배선 CMOS 기술이다.

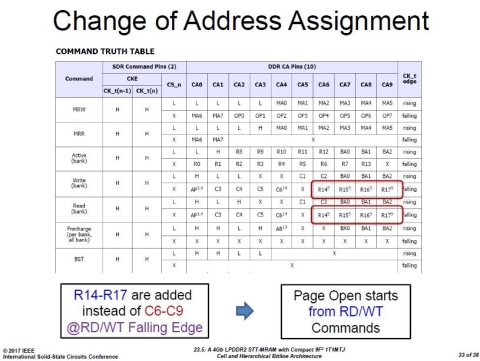

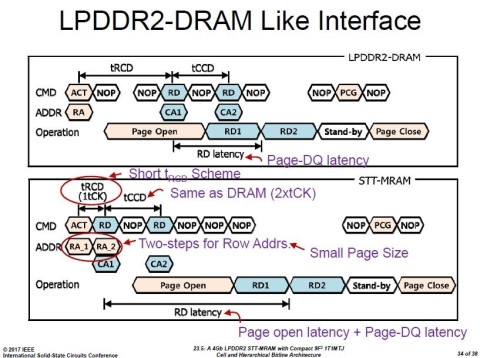

메모리 칩의 사양은 저전력 DRAM(모바일 DRAM)과의 호환성을 의식한 것이다. 입출력 버스는 16bit 혹은 32bit. 입출력 인터페이스는 LPDDR2 인터페이스와 호환성을 갖는다.

다만 행 주소와 열 주소, 동작 타이밍은 약간의 차이가 있다. 우선 행 주소가 많고 열 주소가 적다. 이는 STT-MRAM 페이지 크기가 2Kbit(256B)로 작기 때문이다. 그리고 실제 동작에는 늘어난 행 주소를 2회에 나누어 입력할 필요가 있다. 이 결과 동작 타이밍 차트는 DRAM과 조금 다른 것이다.

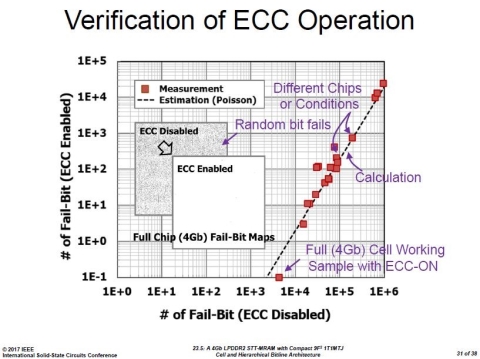

ECC 기능 탑재로 풀비트 동작의 실리콘 다이 취득

메모리 아키텍처에도 몇가지 차이가 있다. 이미 설명했듯이 페이지 크기가 작다. 또 1bit의 데이터 오류를 정정한 ECC(오류 검출 정정)기능을 싣고 있다. 오류 정정 부호는 "(72, 64)해밍 부호". 해밍 부호는 반도체 메모리가 올리는 오류 정정 부호로는 극히 평범한 것이다. 강연에서는 ECC 기능을 선택함으로써 모든 비트가 동작하는 실리콘 다이(양품의 실리콘 다이)를 얻었다고 발혔다. ECC가 있다고 하지만 수직 자기 기록 방식의 STT-MRAM 이라는 제조가 어려운 메모리이기에 4Gbit의 전체 비트가 동작하는 실리콘 다이를 얻을 수 있다는 것은 상당히 드문 일이다.

리던던트 비트의 크기(기억 용량)은 공개하지 않고 있다.

기억 용량당 더 작은 실리콘 다이

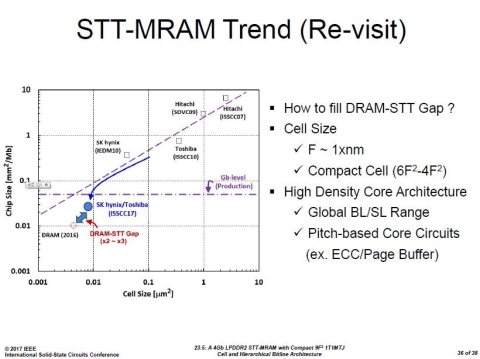

개발한 STT-MRAM은 과거에 학회 등에서 공표되어 온 MRAM에 비하면 극히 높은 기억 밀도를 실현할 수 있다. 4Gbit의 대용량 기억에서 107.5평방mm의 실리콘 다이 면적이란 기존의 연구 개발 상황을 감안하면 경이로운 값이다.

그러나 현실은 만만하지 않다. 같은 기억 용량인 4Gbit의 DRAM 실리콘 다이에 비하면 STT-MRAM의 실리콘 면적은 아직 2배~3배의 크기가 있다. 즉, 이 칩을 양산해서도 제조 비용으로 DRAM을 이길 가능성은 제로다. 제조 원가에 적정으로 생각되는 이윤(마진)을 올리면 판매 가격은 DRAM 보다 훨씬 높아진다. (여기서는 개발 비용은 고려하지 않았다)

제조 비용으로 DRAM과 같은 수준의 근접에는 실리콘 면적을 더욱 낮출 필요가 있다. 강연에서는 가공 치수를 1xnm로 미세화하고 메모리 셀을 더 작게, 코어 아키텍처를 변경하고자 하는 것을 개량 수단으로 꼽았다. 매우 어려운 길이지만 새로운 개량이 계속되기를 기대한다.

출처 - http://pc.watch.impress.co.jp/docs/news/event/1043478.html

TSMC, 5나노 프로세스까지의 기술...

TSMC, 5나노 프로세스까지의 기술...

인텔, 24코어 48스레드 제온 E7-8...

인텔, 24코어 48스레드 제온 E7-8...