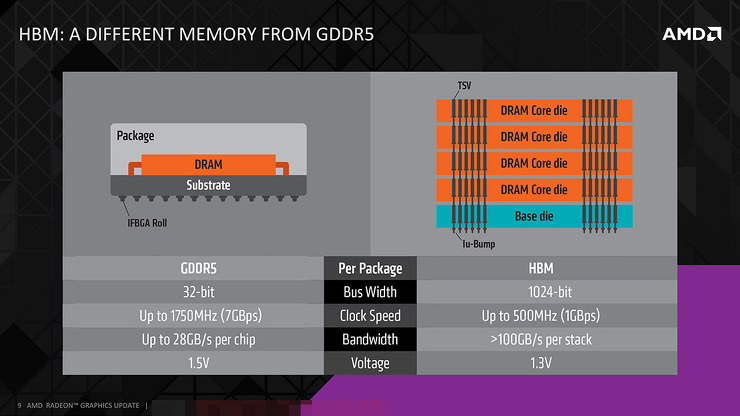

JEDEC은 High Bandwidth Memory(HBM) 규격을 업데이트 한 JESD235를 발표했다.

HBM은 HPC, 서버, 그래픽, 네트워킹 등 광대역과 저전력, 고밀도 탑재가 요구되는 업계용 고속 메모리 규격이다.

새로운 JESD235는 8개의 독립채널로 분할된 1024bit 폭의 인터페이스를 통한 1스택 디바이스당 최대 307GB/s의 대역을 실현한다. 따라서 TSV 기술에 의한 2Hi(2층), 4Hi(4층), 8Hi(8층), 12Hi(12층) 메모리 적층에 대응하며 1스택당 최대 용량은 24GB.

엔비디아의 Tesla 등에 채택되고 있는 4스택 구성의 경우 JESD235는 인터페이스폭 4096bit/합계 대역폭 1228GB/s로 최대 96GB의 V램의 구축이 가능해진다.

이번 규격 갱신은 핀당 대역폭이 2.4Gbps로 확장되어 고밀도 컴퍼넌트용 16Gb 레이어와 12Hi 구성에 대응하는 새로운 옵션 추가 등이 이루어지고 있다.