ARM은 미국 새너제이에서 동사의 기술 콘퍼런스 "ARM Techcon"을 10월 8일~10일까지 개최했다. 첫날 키노트 스피치에서는 차 차세대 Cortex-A 클래스 CPU 코어 아키텍처 "Matterhorn(매터호른/매터폰)의 신 연산 명령이나 Cortex-A코어로의 사이드 채널 어택 대응 보안 기능 실장, Cortex-M의 커스텀 명령 도입, 게임 엔진 Unity의 ARM 코어군에 최적화 등이 발표되었다. 새로운 서버 CPU 코어 IP 등도 컨퍼런스 기간중에 발표될 전망이다.

Arm의 Ian Smythe(Vice President Marketing Operations, Arm)는 Cortex계 CPU 코어의 향후 기술적인 방향에 대해 설명했다.그는 업계의 트렌드로서 반도체 프로세스가 점점 복잡해져 고비용으로 변하고 있다고 지적했다. 그 문제에 대한 확실한 해답은 도메인 스페시피크(영역특화) 컴퓨팅이라고 설명한다.

또 사이버 범죄가 큰 과제가 되고 있어 제품 포커스에서 솔루션 포커스로 바뀌고 있는 것, IP의 경계를 넘어 최적화할 필요가 있음을 지적했다. 그런 문제에 대해 Arm은 시스템적 접근으로 "토탈 컴퓨트(Total Compute)"를 추진한다.

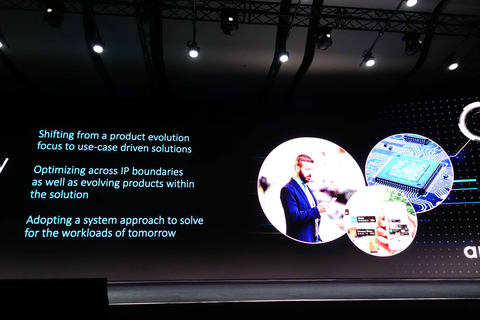

Arm이 토탈컴퓨트라고 말하는 것은 컴퓨팅의 성능을 끌어올릴 뿐만 아니라 보안이나 소프트웨어&툴까지 포괄적인 솔루션의 제안이다. 토탈컴퓨트 자체는 마케팅 캐치프레이즈지만 수요적인 요소를 포함하고 있다.

Matterhorn에서는 새 명령어 집합 ARMv8.6-A 서포트

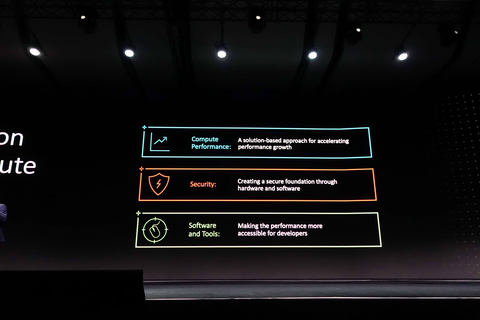

우선 성능 확장이 도메인 스페시픽 확장으로서 심층 학습용 새 명령을 Matterhorn에 도입한다. 새 명령에 의해 기계 학습 매트릭스 연산 성능을 Cortex-A73보다 10배로 끌어올린다.

"기계 학습에서는 Cortex-A75/55에 닷 프로덕트 명령을(SIMD)에 도입했다. Cortex-A76에서는 성능을 2배로 올렸다. 그리고 Hercules 후 세대가 되는 Matterhorn에서는 k, 새로운 명령을 아키텍처에 도입한다. 매트릭스 곱셈(Matrix Multiply), 『 MatMul』라고 부르는 명령으로 CPU의 성능이 더 많이 오른다"고 Smythe는 말한다.

Arm의 Cortex-A/Neoverse 클래스 CPU 명령 세트는 "ARMv8-A", 현재 ARMv8-A는 소수점 아래 버전업이 계속되고 있다. 이번에 발표된 새로운 매트릭스 곱셈 명령 MatMul은 차기 버전의 "ARMv8.6-A"에서 끌어들인다. CPU에 벡터 명령뿐만 아니라 매트릭스 연산형의 명령이 더해지게 된다. NVIDIA가 벡터프로세서인 GPU에 본격적인 매트릭스 연산 유닛 "텐서코어"를 넣은 예와는 조금 다르다.

ARM이 ARMv8.6에서 스캔 매트릭스 명령 MatMul의 실행 유닛은 비교적 소규모 유닛이다.레지스터도 128-bit의 기존 벡터장을 쓴다. 데이터 밀도는 16-bit의 "bfloat16"에서 128-bit 레지스터에 2x4의 bfloat16 값을 다시 1개의 레지스터 2x4의 bfloat16과 곱셈, 그 결과를 32-bit 단정밀도 FP32로서 출력하고 다른 FP32 값과 가산한다. 성능 향상은 현행 Cortex-A77에 비해 5배 정도가 된다.

여기서 핵심은 ARM이 bfloat16을 데이터 포맷으로 채용한 것이다. bfloat16(Brain Floating Point 16)은 뉴럴 네트워크(용도를 전제로 제안된 새로운 부동 소수점 포맷)으로 Google이 채용하고 인텔도 이어지고 있는데 ARM도 2020년 Matterhorn 코어에서 채용한다.

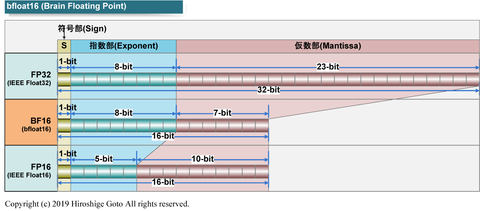

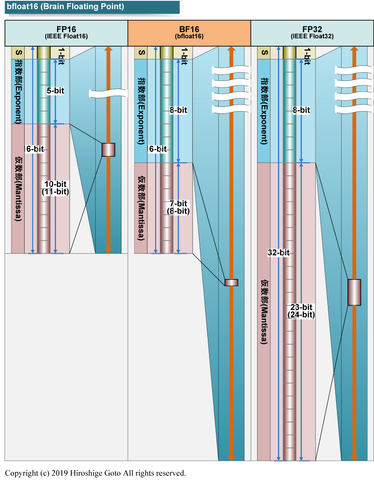

기존의 IEEE 754의 부동 소수점은 FP32(32-bit 단위)가 부호부(Sign)1-bit, 지수부(Exponent)8-bit, 가수부(Mantissa) 23-bit로 구성되어 있다. bfloat16에서는 부호부(Sign)1-bit, 지수부(Exponent)8-bit, 가수부(Mantissa)7-bit와 FP32와 같은 지수부의 다이내믹 레인지를 갖춘다. 데이터 사이즈를 절반으로 하면서 다이내믹 레인지는 FP32와 비슷하다. 다이내믹 레인지가 뉴럴 네트워크에 중요한 적절한 포맷.

ARM은 심층 학습용 프로세서인 "ARM ML" 아키텍처에서는 bfloat16을 채택하지 않는다. 이는 타깃이 추론이기 때문에서 훈련에서 유용성이 높은 bfloat16은 대응하지 않았다. 그러나 CPU 측은 향후 bfloat16을 채용한다. 이는 데이터 센터 전용 Neoverse를 위한 확장으로 보인다.

사이드 채널 공격에 대한 보안 대책

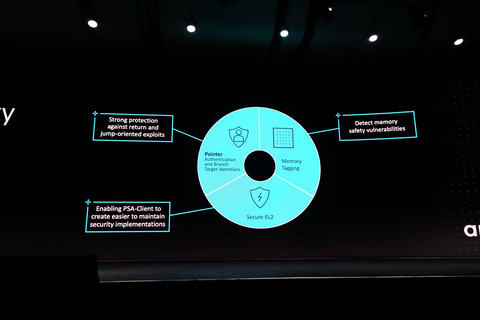

보안에서는 최근 몇 년간 화제인 CPU 아키텍처에 대한 사이드 채널 공격(Meltdown, Spectre등)에 대한 대책이 꼽혔다. ARM은 이 문제에 대해 마이크로 아키텍처 레벨에서 대책을 강구한다. 구체적으로는 "메모리 태깅(Memory Tagging)", "포인터 인증(Pointer Authentication)" 등을 구현한다.

메모리 태깅은 메모리 범위에 4-bit의 태그를 단다. CPU의 메모리 액세스는 접근하는 주소를 저장한 레지스터의 태그와 메모리 태그를 비교한다. 태그는 4-bit로 작기 때문에 재이용되지만 그래도 악의 있는 프로그램의 액세스를 높은 확률로 막을 수 있다.

게임 엔진과의 제휴 발표

그 밖에 Smythe의 세션에서는 소프트웨어 에코 시스템 발전의 일환으로서 게임 엔진 벤더 Unity와의 파트너십이 발표되었다. 지금까지도 Unity의 엔진은 Arm계 SoC에 달리고 있었다.앞으로 양 회사는 파트너십을 발전시켜 보다 최적화가 진행된 소프트웨어와 하드웨어의 통합을 목표로 한다.

구체적으로는 Unity의 렌더링 파이프라인을 Arm 코어에 최적화, 멀티 코어에서의 성능을 발휘하는 멀티 스레드 코드를 생성할 수 있는 "Data Oriented Tech Stack(DOTS)"을 Arm 코어에 최적화, Unity의 AR 솔루션 "AR Foundation"도 Arm 코어의 성능을 이끌어낼 수 있도록 한다.Unity는 Unity 엔진에서 Arm의 뉴럴 네트워크 코어에도 대응한다고 밝혔다.

출처 - https://pc.watch.impress.co.jp/docs/column/kaigai/1211845.html

120Hz, 1.08억화소 지원 삼성 '엑...

120Hz, 1.08억화소 지원 삼성 '엑...

구글이 "양자 초월성"을 달성했다...

구글이 "양자 초월성"을 달성했다...