현재의 DRAM 시장은 2 가지 종류의 사양이 주류가 되고 있다. 하나는 서버나 PC 등에서 사용되고 있는 DDR3 DRAM, 또 하나는 스마트폰이나 미디어 태블릿등의 모바일 기기에 사용되고 있는 LPDDR2 DRAM 이다.

DRAM의 공통 기술 사양은 제조 업체와 사용자 단체로 구성되는 JEDEC이 지금까지 책정해 왔다. JEDEC은 이미 DDR3의 차기 DRAM 사양인 「DDR4」와 LPDDR2의 차기 DRAM 사양인 LPDDR3의 책정을 진행하고 있으며, 모두 2012년안에 상세한 기술 사양이 공표될 예정이다.

● DDR4 DRAM 칩으로 3.3 Gbps를 달성

DDR4 DRAM은 기본적으로 DDR3 DRAM의 2배의 고속화를 실현하는 목적으로 개발된다. DDR3 DRAM의 입출력 핀 당 데이터 전송 속도는 1.6Gbps(1,666Mbps)가 최대지만, DDR4 DRAM은 입출력 핀 당 3.2 Gbps의 데이터 전송 속도를 실현한다.

DDR4 DRAM은 우선적으로는 서버에 도입될 전망이다. 도입 시기는 빠르면 내년(2013년). PC 시장의 도입은 2014년 이후가 될것이라고 전망되고 있다.

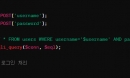

[ 4Gbit DDR4 DRAM의 실리콘 다이 사진과 사양(최종 제품은 아니다). 실리콘 다이 면적은 76mm² ]

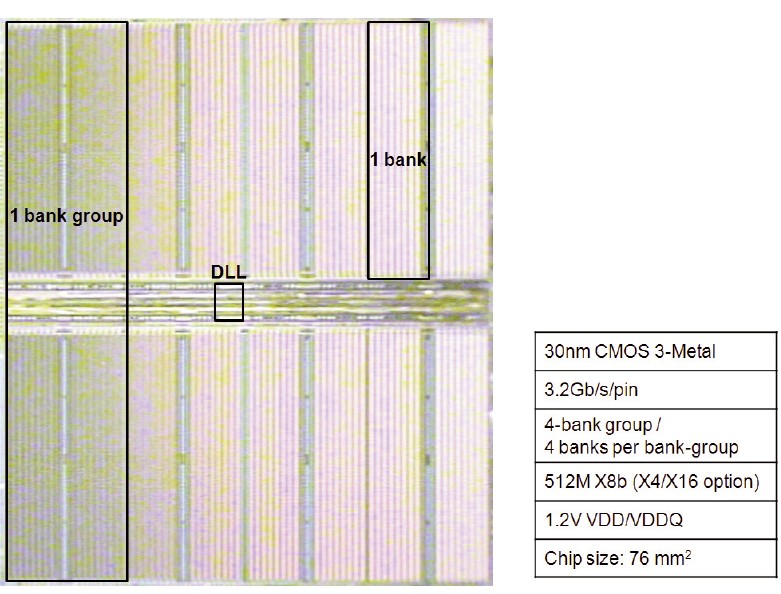

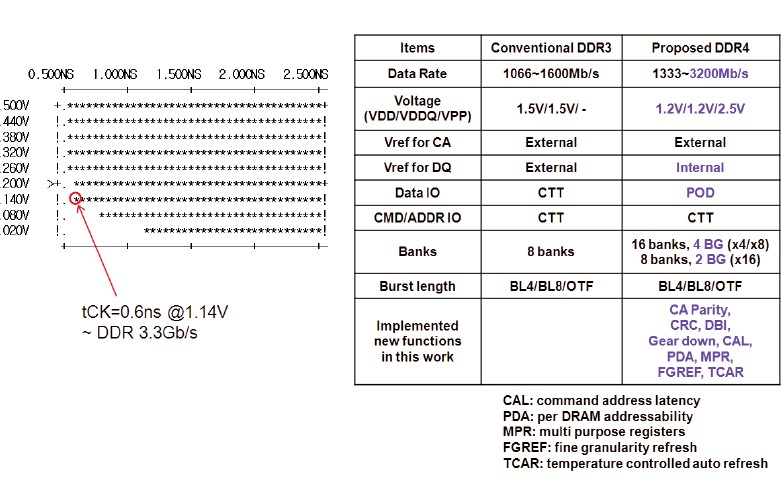

[ 데이터 전송 속도 측정 결과와 DDR3 및 DDR4의 사양. 청색 부분이 DDR3에서 변경된 점 ]

삼성전자는 작년 1월 4일에 DDR4 DRAM를 개발했다고 발표했다. 또 ISSCC 2012에서는 삼성전자와 하이닉스가 각각 DDR4 DRAM의 개발 성과를 발표했다. 삼성전자가 개발한 것은 4Gbit 용량의 DDR4 DRAM 이다. 제조 기술은 30 나노미터 CMOS, 3층 금속 배선 기술. 전압은 1.2 V.

개발 칩은 높은 성능을 나타냈다. 전압이 1.14 V 일때 입출력 핀 당 3.3 Gbps의 데이터 전송 속도가 확인됐다. DDR4 DRAM의 양산에는 30나노미터가 아닌 한층 더 미세한 20나노미터의 제조 기술이 사용된다. 삼성전자가 30 나노미터 기술의 개발 칩으로 DDR4의 목표 사양인 3.2 Gbps를 넘어선 것은 높게 평가할 수 있는 부분이다.

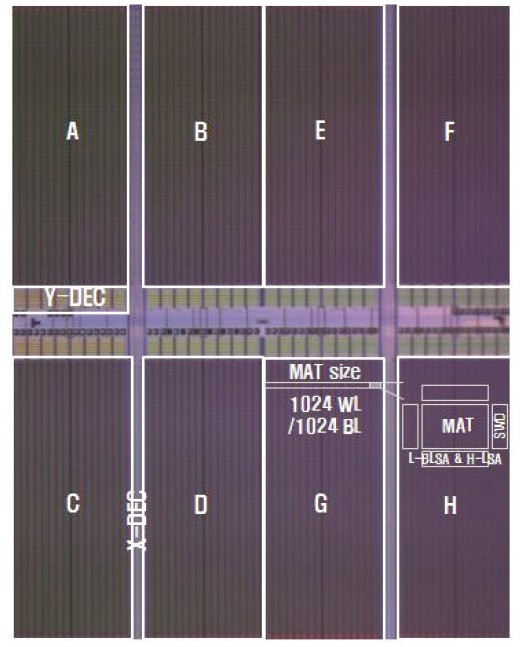

[ 2Gbit DDR4 DRAM의 실리콘 다이 사진 사양(단 최종 제품은 아니다) 다이 면적은 불명 ]

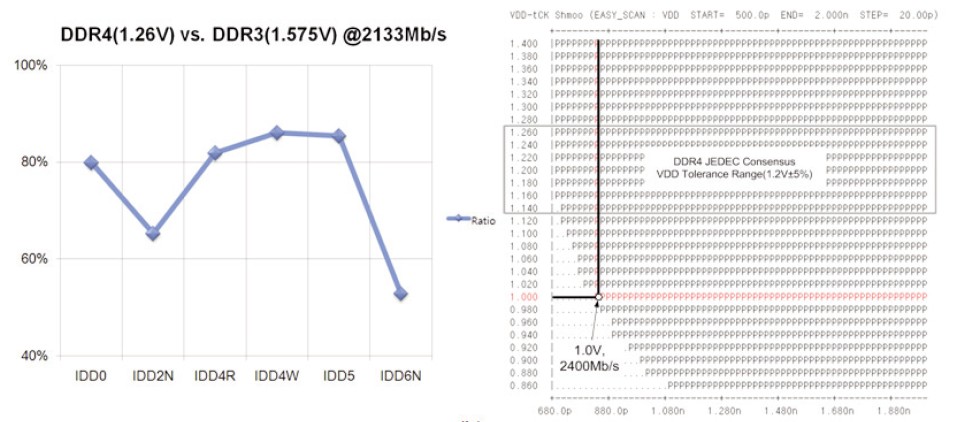

[ 개발 칩(DDR4)와 DDR3 DRAM의 소비 전력 비교와 데이터 전송 속도의 측정 결과 ]

하이닉스가 개발한 것은 기억용량 2Gbit의 DDR4 DRAM 이다. 제조 기술은 38 나노미터의 CMOS, 3층 금속 배선 기술. 전압은 1.2 V.

개발 칩과 DDR3 DRAM을 2,133 Mbps의 데이터 전송 속도로 동작시켰을 때 개발 팁의 소비 전력은 DDR3의 8할 정도로 감소되고 있었다. 또 전압이 1.0 V 일때 입출력 핀 당 2.4 Gbps의 데이터 전송 속도로 동작하는 것을 확인했다. 38 나노미터 기술인 것을 고려하면 꽤 높은 성능을 발휘하고 있다고 말할 수 있다

● 406 mW로 6.4 GB/sec를 실현한 LP DDR3

LPDDR3 DRAM은 기본적으로 LPDDR2 DRAM의 고속형 모델이다. 이론적으로는 LPDDR2의 2배의 데이터 전송 속도를 달성할 수 있다. 모바일 기기로의 실제 탑재는 2013년에 시작될 것이라고 예상된다.

[ 실리콘 다이 면적 30.9mm² 의 4Gbit DDR3 DRAM 다이 사진 ]

ISSCC 2012에서는 삼성전자가 LPDDR3 DRAM의 개발 성과를 발표했다. 용량은 4Gbit, 제조 기술은 30나노미터, 전압은 1.2V, IO 32bit로, 전압이 1.05 V로 내려 갈때까지 1.6 Gbps의 데이터 전송 속도로 동작했다.

이 외 하이닉스가 실리콘 다이 면적이 30.9mm²의 작은 4Gbit DDR3 DRAM를 발표했다. 제조 기술은 23 나노미터 CMOS, 2층 동배선, 1층 알루미늄 배선. 전압은 1.2 V로, 저 전압판 DDR3의 「DDR3U」에 상응한다. 제조 기술이 23 나노미터로 미세화된 것이 실리콘 다이 면적의 축소에 기여했다. 상당히 좋은 가격 경쟁력을 갖출 것으로 보여진다.

ISSCC 2012에서 DRAM 칩을 발표한 것은 삼성과 하이닉스 모두 한국 DRAM 메이커였다. 다른 대기업인 엘피다 메모리나 Micron Technology등의 발표는 없었다. 작년 ISSCC 2011에서도 DRAM 칩을 발표한 것은 한국의 삼성과 하이닉스 뿐으로, 한국이 DRAM 시장을 주도하고 있는 점을 다시 한번 확인할 수 있다.

태블릿 시장 및 엔비디아 쿼드코...

태블릿 시장 및 엔비디아 쿼드코...