미국 IBM은 뇌에서 영감을 얻은 비 노이만형 컴퓨터 아키텍처 시냅스 칩(SyNAPSE)을 발표했다.

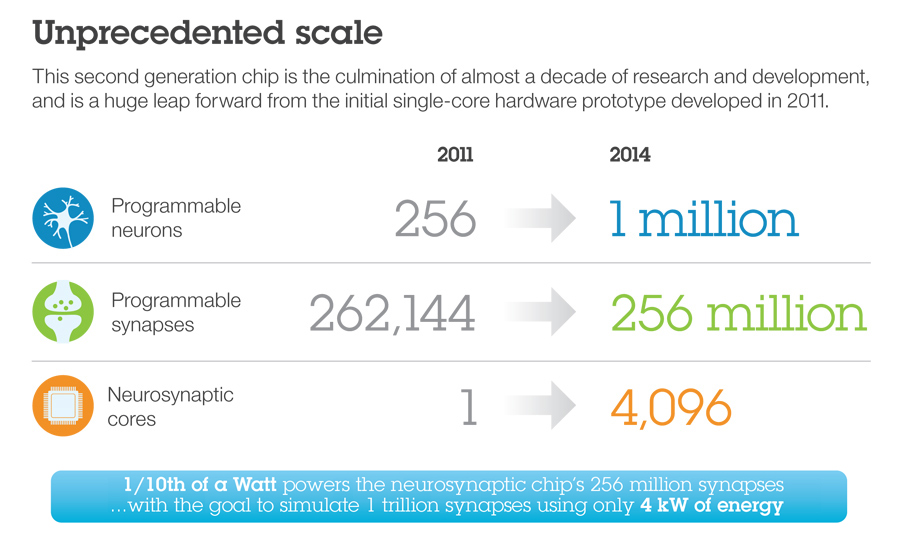

시냅스 칩(SyNAPSE)은 고밀도 온-칩 메모리와 전력 누수가 적은 트랜지스터로 구성된 삼성전자의 28나노 공정으로 백만개의 프로그래밍이 가능한 뉴런과 2억 5600만개의 프로그래밍이 가능한 시냅스로 1와트시 매초 460억의 시냅스틱 운영 스케일을 달성하고 있다.

54억개의 트랜지스터로 구성된 이 칩은 현 시점에서 지금까지 제조된 칩 가운데 최대 규모의 CMOS 칩으로 생물학적 실시간 가동시에는 70mmW의 매우 작은 소비 전력으로 동작한다.

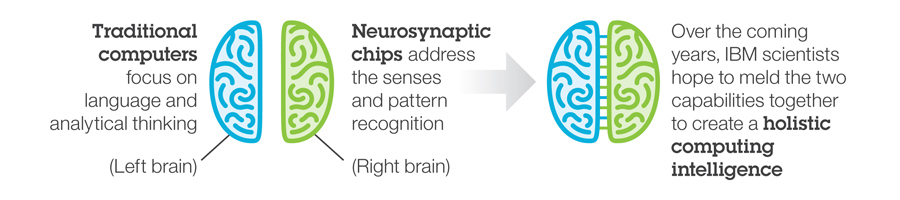

IBM의 이번 시냅스 칩은 인지 컴퓨팅에 중요한 첫 걸음으로, 이번 성과는 코넬 테크(Cornell Tech)와 공동 논문으로 사이언스지(Science) 최신호에 게재되고 있다.

새로운 접근의 뉴로 사이언스에서 영감을 얻은 2세대 아키텍처 칩은 10년에 가까운 연구 개발의 집대성으로서, 아키텍처는 4096개의 디지털 분산 뉴로 시냅틱 코어 온-칩 2차원 구동 네트워크를 갖고 있다. 또한 각각의 핵심 모듈은 메모리, 계산, 커뮤니케이션을 통합하여 필요시에만 작동하는 이벤트 구동 방식으로 병렬 형태로 동작한다.

이러한 칩들은 인간의 대뇌 피질처럼 자유롭게 확장이 가능한 인터칩 인터페이스를 통해 상호 연결하여 확장이 가능한 뉴로 모픽(인간의 뇌를 닮은) 시스템 설립을 가능하게 하며 IBM은 시냅스 칩의 확장성(Scalability)을 실증하기 위해 1600만개의 프로그래밍이 가능한 뉴런과 40억개의 프로그래밍이 가능한 시냅스로 구성된 16칩 시스템도 공개하고 있다.

Traditionally, faster processing has always meant greater power consumption, but IBM's new SyNAPSE chip flips that paradigm on its head

이 프로젝트는 미국 국방부의 국방 고등 연구 계획국(DARPA)가 2008년부터 The Systems of Neuromorphic Adaptive Plastic Scalable Electronics(통칭 SyNAPSE = 신경 형태학적 전자 공학 시스템) 프로그램의 0단계 1단계 2단계 3단계로 약 5300만 달러를 지원하고 있으며 현재 Cornell Tech, iniLabs 등과 공동으로 연구하고 있다.

IBM은 "1kw 에너지로 작동하며 100억개의 뉴런과 100조개의 시냅스가 내재된 2리터 이하의 부피를 가진 뉴로 시냅틱 칩 시스템" 구축을 다음 목표로 하고 있다.