하스웰 eDRAM의 수수께끼가 풀렸다

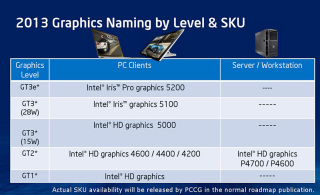

Haswell(하스웰) eDRAM의 실체가 보이고 있다. Haswell에는 GPU 코어를 최대로 구성한 GT3 구성에 eDRAM을 추가한 GT3e가 있다. GT3e 를 탑재한 Haswell은 다른 Haswell 시리즈와는 다른 별도 다이로 CPU 측은 4 CPU 코어에 6MB의 L3캐시 구성이다. 이 eDRAM에 대해서는 미국에서 일부 언론에서 설명한 적이 있지만 일본에서는 기술 정보가 설명되지 않고, 수수께끼 상태 그대로였다. 그러나 COMPUTEX의 몇몇 업계 정보 소스에서 eDRAM의 정체와 Intel의 의도가 드러났다.

Haswell GT3e의 eDRAM은 최대한의 하드웨어 제어 L4 캐시다. 그래픽용 메모리 계층을 더하는 것이 아니라 CPU+GPU 전체에 대용량 선택 패키지 L4 캐시를 더한 것이 GT3e 지만 Intel은 eDRAM자체를 자사의 22나노 프로세스에서 제조한다. 1G-bit칩 인터페이스는 시리얼 전송, 메모리 대역은 한쪽 방향만 50GB/sec 클래스라고 한다.

GT3e 버전 Haswell은 eDRAM 캐시 때문에 다이 쌍방향으로 512-bit의 직렬 인터페이스를 위한 대량의 SerDes를 싣고 수 메가바이트의 태그 SRAM을 싣고 있다고 본다. 또 CPU 내부 버스의 구성도 일반 Haswell과 사뭇 다르다고 본다.

Haswell 4코어+GT3e의 eDRAM의 사양이 나타내는 것은 Intel이 메모리 계층의 개혁에 진지하게 임하고 있는 것으로 그 이유는 명백하여 더 이상 칩의 연산 성능을 끌어내려면 메모리 대역을 향상시킬 필요가 있기 때문이다. 앞으로 CPU나 GPU의 코어를 늘리려고 하면 메모리 대역을 기존 DRAM 솔루션에서 늘릴 수 있는 이상으로 확대할 필요가 있다.

그 때문에 이번에 Intel은 메모리를 자사에서 생산했다. 이 뜻은 크다.

우선 Intel은 프로세서에 필요한 메모리 대역을 얻기 위해서라면 메모리 칩을 자사에서 개발 / 제조하는 것도 불사하지 않는다는 것이 밝혀졌다. 메모리 사업에 참가하고 싶다기보다 자사의 주력인 프로세서 사업을 위해 메모리가 필요하다고 판단하고 있는 것이다. 이제 논리 칩만 만들어서는 논리 칩의 성능을 올리기가 어렵다고 생각하는 듯하다.

프로세서를 부스터에 사용할 메모리는 이번에는 DRAM 기술이었다. 그러나 DRAM의 미세화 한계가 임박하고 있어 장기적으로는 다른 대용량 메모리 기술로 생산을 진행할지도 모른다. Intel이 메모리에는 별로 손을 대지 않는다는 생각은 이제 틀렸다.

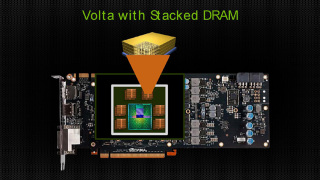

그러나 Haswell 패밀리 중의 궁극적인 솔루션인 GT3e 구성도 결코 Intel이 시도한 완성형은 아니라는 것도 명백하다. 현재 하이 퍼포먼스 프로세서는 선택 패키지에 고속 기억 장치를 탑재하는 방향으로 향하고 있다. Intel 뿐 만 아니라 AMD, NVIDIA도 기본적으로는 같은 방향으로 가고 있다. 그러나 거기에는 과제가 여러가지 있고, 어떻게 해결할지는 아직 결론이 나오지 않았다. 한 동안은 각사의 시행 착오가 계속될 것이다.

22나노 프로세스의 인텔 eDRAM기술

Haswell GT3e 패키지에 실려 있는 eDRAM은 Intel의 22나노 공정으로 제조된다. Intel은 6월 11일부터 교토에서 개최되는 "VLSI Symposium(2013 Symposium on VLSI Technology and Circuits)"에서 22나노 공정 eDRAM 기술을 발표할 예정으로 Haswell의 eDRAM은 이 기술을 사용하고 있다고 본다. 참고로 이 컨퍼런스에서는 Intel의 통합 전압 레귤레이터 기술(온 다이 DC-DC 변환기 부분)도 발표될 전망이다.

DRAM 제조 프로세스 기술을 알고 있으면 22나노의 DRAM 으로 알고 놀랄지도 모른다. DRAM의 프로세스는 겨우 30나노 대에서 20나노 프로세스로 이행이 진행되기 시작했을 뿐이기 때문이다. 노드의 숫자로서 22나노의 인텔 DRAM은 완전히 최첨단이다.

그러나 그건 어디까지나 디스크 리트의 DRAM 칩 제조 프로세스 기술의 얘기다. Intel이 발표한 것은 22나노 로직 과정에 혼재하는 eDRAM 기술로 DRAM과 로직 프로세스는 노드 숫자의 근거가 달라 이 때문에 같은 척도로 비교할 수 없다.

실제 메모리 셀의 크기로 보면, Intel의 22나노 eDRAM은 디 클리트 DRAM의 30~20나노 다이와는 크게 다르다. Intel의 eDRAM 메모리 셀 크기는 0.029 평방μm 으로 이는 2007년 전후의 하프 속도로 60나노 프로세스 다이의 디스크 리트 DRAM 메모리 셀 크기에 상당한다. 즉, Intel의 eDRAM도 eDRAM의 상례로서 공간 밀도는 단위의 DRAM 칩보다 훨씬 낮다. 디스크 리트 DRAM의 최첨단과는 밀도가 다른 셀 크기도 다르다.

Intel의 22나노 eDRAM은 128M-bit의 메모리 매크로 기반으로 메모리 밀도는 17.5M-bit/제곱mm. 이때부터 역산하면 Haswell GT3e에 실려 있는 1G-bit의 eDRAM 칩의 메모리 매크로 구역은 58.5kmm. GT3e의 eDRAM은 약 80kmm 이상의 다이로 인터페이스에 30% 미만을 쓰고 있다고 생각하면 거의 계산이 맞다.

직렬 전송 DRAM 인터페이스

eDRAM 인터페이스는 시리얼 전송 즉, Haswell GT3e에 얹혀 있는 것은 직렬 인터페이스 DRAM 이다. Intel은 과거 DRAM인터페이스를 직렬로 삼는 방안을 업계에 제안했다. 여기서 Intel의 직렬 DRAM구상이 결실을 맺은 것이다.

eDRAM이 직렬 인터페이스인 것은 Haswell GT3e의 서브 스트레이트 상의 eDRAM 칩의 배치에서도 알수 있다. eDRAM 칩은 GT3e의 다이에 달라 붙어 배치되고 있다. 병렬 인터페이스에서 일반적으로 필요한 배선을 할 여지가 없는 배치다. 배선이 불 필요한 인터페이스가 아니면 이 배치는 어렵다고 추측된다.

인터페이스 폭은 한쪽 방향이 256-bit로 쌍방향에서는 512-bit 라고 한다. 디퍼렌셜(차등)신호로 보이기 때문에 핀 수는 데이터에만 1,000핀 이상으로 엄청난 숫자고 이 배선층을 포함해서인지 Haswell GT3e는 서브 스트레이트가 두텁고 통상보다 층수가 늘어나고 있다.

다이 면적을 차지하고 있을 것으로 추정되는 태그 RAM

Haswell GT3e 구성의 다이는 eDRAM을 최대한 하드웨어적인 캐시로 제어되는 것으로 확인되었다. 여기서 나온 큰 의문은 태그 RAM(TagRAM)이다. 캐시로 쓴다면 권한의 캐시 태그를 거둔 메모리가 필요하다. 캐시 태그는 캐시 메모리에 모든 메모리 주소의 데이터가 들어 있는지를 나타내는 태그다.

캐시 태그를 거두려면 일정량의 태그 RAM용 메모리가 필요하다. 그리고 캐시의 성능을 생각하면 태그 RAM은 Haswell GT3e의 본체 측의 다이로 통합되고 있을 것이다. 그렇지 않으면 태그 RAM 액세스만으로 전력 소비가 늘고, 레이턴시가 길어진다. 그리고 CPU 자체에 포함하면 SRAM 이다.

그러고 보면 Haswell GT3e의 큰 다이의 수수께끼도 풀린다. 이전 Haswell GT3e의 다이는 사우스 브리지 칩이 통합되어 대형화되고 있을 가능성이 있다고 말했지만 이것은 실수로, 다이를 더 크게 하는 것은 아마도 태그 RAM이다. 왜냐하면 캐시 메모리 양이 커지면 태그 RAM도 늘어나기 때문이다. 1Gbits 즉 128MB 캐시를 태그 RAM으로 준비하면 태그 RAM은 상당한 면적을 차지 할 것이다.

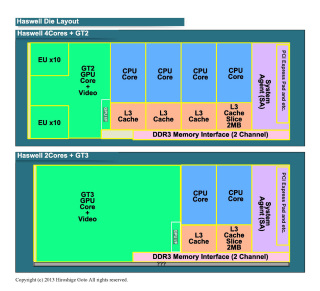

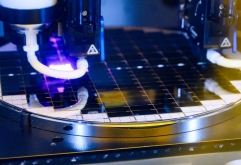

아래는 2 CPU코어에 GT3 GPU 코어의 "2+3"구성의 Haswell과 Haswell GT3e를 늘어놓은 사진이다. 이제 계산하면 Haswell의 2코어+GT3의 다이 면적은 약 180kmm, Haswell 4코어+GT3e의 다이는 약 260kmm 초과.

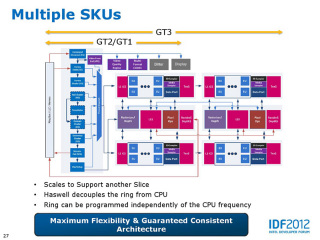

재미 있는 것은 2코어+GT3의 다이가 노출된 4코어+GT2의 다이로 종횡으로도 길이가 다르다는 점. 좁은 분은 동일한 것 같은데 조금만 넓다. 그 이유는 모르지만 DRAM 인터페이스 방향으로 차이가 있을지 모른다. 두 다이의 예상되는 내부 골격은 다음과 같다. 잘못알고 있을 가능성은 있지만 큰 틀은 아래와 같이 되어 있다고 추측된다.

왼쪽의 다이에 따라 Intel의 GT3 GPU코어의 대략적인 크기를 알 수 있다. GT3은 GT2에 비해 약 80%정도 커지고 있다고 본다. GT3는 미니 GPU와 할 조각이 2층으로 되어 있으므로 이 비율은 타당하게 보인다.

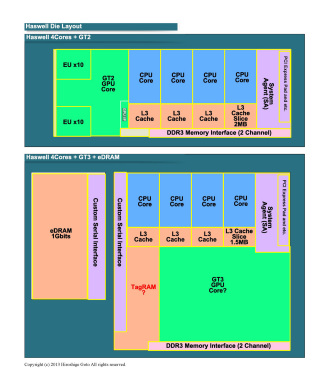

여기에서 약 260kmm의 Haswell 4+3(4코어+GT3)의 다이로 각 구성 요소를 배치해 보자. 177kmm의 4+2(4 CPU코어+GT2 GPU코어) GT3에 의한 GPU코어의 증가분을 더한 크기보다 Haswell 4+3(4코어+GT3)의 다이 크기가 훨씬 크다. Haswell 4+3에는 플러스 알파에서 다른 유닛이 더해져 있을 것이다. 참고로 Haswell 4+3(4코어+GT3)는 L3캐시가 6MB로 4+2의 통상의 8MB의 L3 캐시보다 L3 영역이 작다.

물론 Haswell GT3e에는 eDRAM 사이의 직렬 인터페이스가 어우러진다. eDRAM 측의 인터페이스는 약 20kmm 이상으로 같은 Intel의 22nm프로세스(다만 SoC프로세스). 이 정도 분량의 면적을 인터페이스로 해도 아직 Haswell GT3e의 다이가 크다. 물론 eDRAM의 컨트롤러도 추가되지만 그다지 면적은 받지 않을 것이다. 그래서 나머지 면적의 어느 정도의 부분이 태그 RAM 일 가능성이 높다.

Intel이 eDRAM 캐시에도 64-byte 캐시 라인을 유지하고 있다면 태그 RAM 용량은 단순 계산으로 수십 MB다. 그러나 캐시 효율을 떨어뜨리는 것을 각오로 캐시 라인을 넓게 취하면 태그 RAM의 양을 줄이거나 여러가지 방법은 있다. 실제의 다이 크기를 꼼꼼히 비교하면 태그 RAM의 크기는 수 MB 정도로 보인다. 단순히 공간을 4+2 캐시 면적과 비교하면 8~10MB 정도 분 자리가 생긴다.

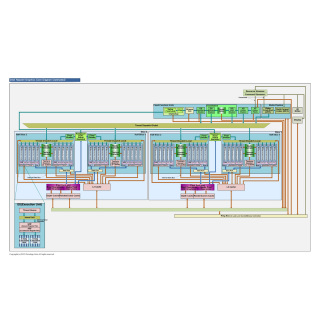

위 그림은 4+3의 쓸데없는 공간이 태그 RAM 이라고 가정한 그림이다. 그러나 면적비가 옳았다고 해도 배치는 크게 다를 것이다. 보통 태그 RAM을 1개의 링 스톱에 배치하면 거기에 액세스가 집중돼 버린다. 예를 들어 태그 SRAM과 eDRAM 인터페이스를 분산해 복수의 링 신호에 접속하는 등의 구성을 취하고 있을 가능성도 있어 그 경우에는 링의 토폴로지가 기존 Haswell과 크게 달라진다.

하스웰의 무거운 eDRAM 솔루션

이렇게 거칠게 계산해도 eDRAM 솔루션의 Haswell 이 꾀 "무거운" 제품임을 알수 있다. 다이 크기에서는 32나노의 Sandy Bridge의 216kmm 보다 훨씬 크다. 경제성은 매우 나빠 보이며 게다가 사용자 지정 DRAM 까지 밀봉하고 있다.

참고로 Intel은 메모리 대역을 올리기 위한 eDRAM을 CPU 다이로 통합하지 않았다. 대역을 올린다면 CPU 다이로 통합한 것이 소비 전력적으로도 유리하다. 그런데도 논리 칩에 포함될 수 있는 eDRAM을 디스크 리트 DRAM과 같이 사용하고 있다.

Intel이 eDRAM을 CPU에 통합하지 않는 이유는 몇가지로 생각된다. 우선 일반적으로 eDRAM을 사용하는 경우는 프로세스가 복잡하게 되기 때문에 고속 CPU에 통합하는 것은 위험 부담이 크다. 또 eDRAM이 논리 과정에 맞춰 스케일 다운할 가능성이 매우 낮은 것도 큰 요인일 것이다. 22나노 프로세스에서 eDRAM을 통합해도 다음 프로세스 세대에서는 통합되지 않을지도 모른다. 통합하더라도 논리처럼 스케일 다운하지 않을 가능성이 높다. 그래서 2년마다 첨단 프로세스로 이행하는 메인 스트림의 제품에는 통합이 적합하지 않다.

가장 특수한 제품의 통합은 있다. 예를 들면 하이엔드 서버용이나 Atom 계통의 모바일용 등으로 일부 eDRAM의 영입 가능성이 없는 것은 아니다. 서버용 CPU는 프로세스의 이행이 늦고, Atom형이라면 eDRAM에서 부가 가치를 더하기 쉽다.

보도 - http://pc.watch.impress.co.jp/docs/column/kaigai/20130610_602912.html

![[All Around AI 1편] AI의 시작과 발전 과정, 미래 전망 우리 삶을 혁신적으로 바꾸고 있는 인공지능(Artificial Intelligence, AI). AI를 알고, 이해하고 또 활용하고 싶은 이들을 위해 <AAA - All Around AI>에서 AI 기술에 대한 모든 것을 알려드립니다. 1화에서는 인공...](https://raptor-hw.net:42215/xe/files/thumbnails/198/205/241x165.crop.jpg)

![[All Around AI 1편] AI의 시작과 발전 과 [All Around AI 1편] AI의 시작과 발전 과 by 인공지능](https://raptor-hw.net:42215/xe/files/thumbnails/198/205/262x75.crop.jpg)