Advanced Micro Devices plans to describe some of the features of its next-generation mobile microprocessor at the International Solid-State Circuits Conference (ISSCC) in early February, 2010. The company will not disclose all the details, which is logical, considering that its 32nm central processing units (CPUs) are only due in 2011, but some of the capabilities may be rather interesting.

One of the documents to be discussed during the ISSCC covers “a 32nm core capable of data rates above 3GHz and power consumption variable from 2.5 to 25W,” reports EETimes web-site.

"The 32nm implementation of an AMD x86-64 core occupying 9.69mm2 and containing more than 35 million transistors (excluding L2 cache), operates at frequencies >3GHz. The core incorporates numerous design and power improvements to enable an operating range of 2.5W to 25W and a zero-power gated state that make the core well-suited to a broad range of mobile and desktop products," the official document reads.

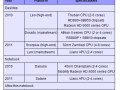

AMD did not state which of its x86-64 cores it plans to describe, which adds a mystery to the content. There are three major 32nm products incoming from AMD:

32nm design based on high-end Bulldozer micro-architecture, which will operate at 3GHz or higher clock-speeds.

Low-power code-named Bobcat processor designed specifically for environments that count every watt of power.

Highly-integrated Llano processor that features 4 x86 cores and 480 stream processors for graphics and stream computing on the same piece of silicon.

Based on transistor count and the size of the die, it can be assumed that AMD will be demonstrating details about Llano processor's x86 engines, even though it is relatively strange that the company decided to once again redesing its K10.5 design to fit it into a highly-integrated chip.

The media report claims that a big chunk of AMD’s paper will focus on circuit techniques the company uses to lower power consumption and leakage of the core. For instance, the core's L1 cache uses 8T memory cells to support low supply voltages, the processor also uses a power gating ring that takes advantage of isolated substrates used in the company's silicon-on-insulator technology to provide a near-zero power off state.

Based on the die shot displayed by AMD earlier this month, the first Fusion processor from AMD - Llano - will feature 4 x86 cores that resemble those of Propus processor (AMD Athlon II X4) with 2MB of L2 as well as 6 SIMD engines (with 80 stream processors per engine) that resemble those of Evergreen graphics chip (ATI Radeon HD 5800); PC3-12800 (DDR3 1600MHz) memory controller, possibly, with some tweaks to better serve x86 and graphics engines.

AMD Bobcat x86 core is due to be released in 2011 as part of AMD Brazos platform and AMD Ontario accelerated processing unit (APU, a microprocessor featuring graphics processing unit on the same piece of silicon and/or substrate). According to AMD, Bobcat chips will feature x86-64, virtualization, SSE, SSE2, SSE3 technologies and will be single-threaded with out-of-order execution. The actual Ontario microprocessor will be able to offer 90% of today’s “mainstream performance” in less than half of die area.

http://xbitlabs.com/

![뚜따에 진심인 형+과학자코스프레+현미경을구입했어 [정종철] 뚜따에 진심인 형+과학자코스프레+현미경을구입했어

CPU 뚜따 교육자료ㅋㅋ](https://raptor-hw.net:42215/xe/files/thumbnails/739/203/241x165.crop.jpg)