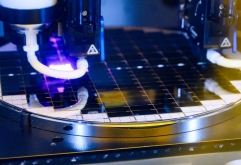

미국 웨스턴 디지털(Western Digital)은 1월 30일, 제5세대 3D NAND 플래시에 해당하는 BiCS5 개발에 성공했다고 발표했다.

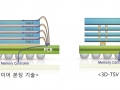

개발한 BiCS5는 메모리 홀 기술이 제2세대로 이행되고 프로세스나 3D NAND 셀이 개선되면서 셀 배열의 밀도가 크게 향상됐고, 더불어 셀의 적층 수도 앞선 세대 BiCS4의 96단에서 112단으로 증가했다.

이로써 웨이퍼당 비트 수가 최대 40% 증가해 비용을 줄이고 설계 개선이 이뤄지며 읽기/쓰기 성능이 최대 50% 고속화했다고 밝혔다.

BiCS5는 1셀당 3bit의 데이터를 기록하는 TLC(Triple Level Cell)와 4bit를 기록하는 QLC(Quadruple Level Cell)를 이용하여 제조되며 TLC 512Gbit 칩의 초기 생산을 이미 시작했고, 본격적인 양산은 2020년 하반기를 예정하고 있다.

![[All Around AI 1편] AI의 시작과 발전 과정, 미래 전망 우리 삶을 혁신적으로 바꾸고 있는 인공지능(Artificial Intelligence, AI). AI를 알고, 이해하고 또 활용하고 싶은 이들을 위해 <AAA - All Around AI>에서 AI 기술에 대한 모든 것을 알려드립니다. 1화에서는 인공...](https://raptor-hw.net:42215/xe/files/thumbnails/198/205/241x165.crop.jpg)

![[All Around AI 1편] AI의 시작과 발전 과 [All Around AI 1편] AI의 시작과 발전 과 by 인공지능](https://raptor-hw.net:42215/xe/files/thumbnails/198/205/262x75.crop.jpg)