ARM의 big.LITTLE 기술의 공식적인 첫 채용

삼성전자는 2013년 1월 라스베가스에서 개최된 2013 International CES의 기조 강연에서 모바일 전용의 차기 고급형 프로세서 Exynos 5 Octa를 발표했다. Exynos 5 Octa는 처음으로 ARM의 소비 전력 최적화 기술인 big.LITTLE= 빅리틀을 탑재한 프로세서로, 4개의 빅코어(ARM Cortex-A15 코어)와 4개의 리틀 코어(ARM Cortex-7 코어)를 작업 부하량에 따라 스위칭하여 소비 전력을 최적화한다. 이 기술 내용이 ISSCC2013에서 공표됐다.

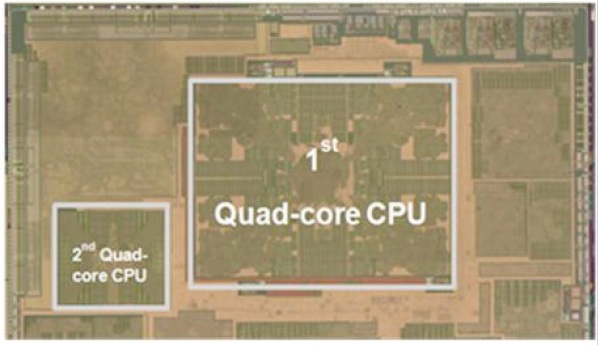

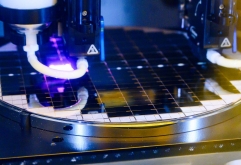

엑시노스5 옥타의 실리콘 다이 사진. 실리콘 다이 면적은 공개하지 않고 있다

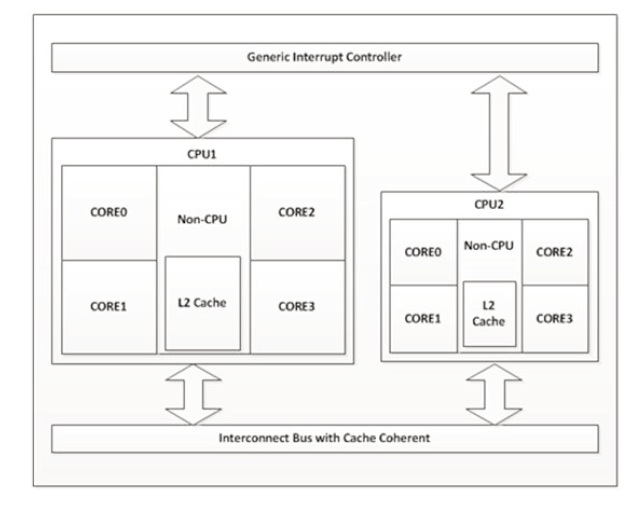

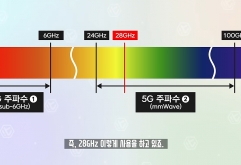

개발한 프로세서의 제조 기술은 28나노 HKMG 트랜지스터를 적용한 CMOS 기술이다. 강연에서는 Cortex-A15 코어군의 CPU를 1st Quad-Core CPU 혹은 CPU1, Cortex-A7 코어군의 CPU를 2nd Quad-core CPU 혹은 CPU2 라고 호칭하고 있었다. CPU1의 실리콘 면적은 19평방mm, CPU2의 실리콘 면적은 3.8평방mm의 차이가 있고, 프로세서 전체의 실리콘 다이 면적은 공표하지 않았다. 또 주변 회로에 어떠한 기능이 탑재되고 있는가에 대해서도 모두 공개하지 않았다.

1st Quad-Core CPU 혹은 CPU1의 동작 주파수는 200MHz ~ 1.8GHz. 1차 캐쉬는 32KB의 명령 캐쉬와 32KB의 데이터 캐쉬, 2차 캐쉬는 2MB의 데이터 캐쉬로 구성, 2nd Quad-core CPU 혹은 CPU2의 동작 주파수는 200MHz ~ 1.2GHz. 1차 캐쉬는 32KB의 명령 캐쉬와 32KB의 데이터 캐쉬, 2차 캐쉬는 512KB의 데이터 캐쉬로 구성된다.

기본적인 동작 원리는 "2nd Quad-core CPU 혹은 CPU2가 상시 동작하고, 필요 상황에 따라서 1st Quad-Core CPU 혹은 CPU1 으로 스위칭 된다" 라는 것이다. 구체적인 DMIPS의 값은 공표하고 있지 않지만, CPU1은 CPU2의 1.8배의 DMIPS를 낼 수 있다고 설명했다. 동작 주파수당 소비 전력은 CPU2가 CPU1의 약 6분의 1.

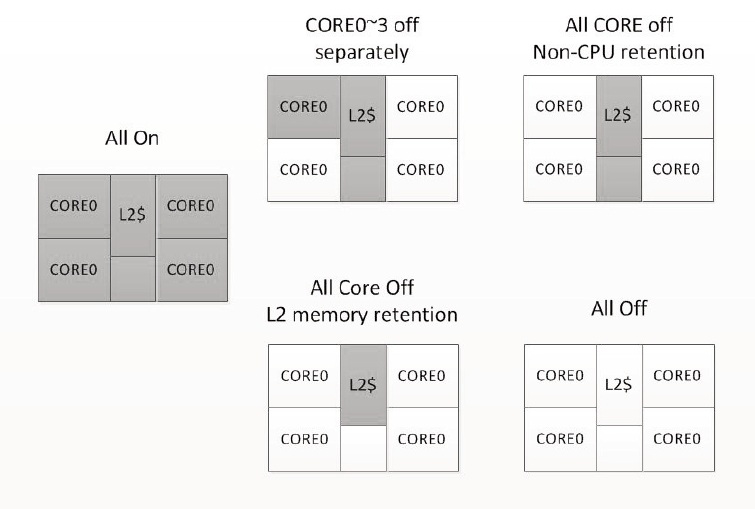

또, 4개의 CPU 코어는 독립적으로 전력을 온/오프 할 수 있는 것 외에 2차 캐쉬만을 동작하게 하여 데이터를 보관 / 유지하고, 4개의 CPU 코어 모두를 정지시키는 모드도 갖춘다. 다만 대기시 소비 전력과 동작시 소비 전력은 분명히 밝히지 않고, 이러한 방식이 어느 정도의 효과를 나타내는지도 확인되지 않았다.

CPU 코어와 2차 캐쉬의 파워게이팅

Exynos 5 Octa 아키텍쳐

보도 - http://pc.watch.impress.co.jp/docs/news/event/20130225_589171.html

![[All Around AI 1편] AI의 시작과 발전 과정, 미래 전망 우리 삶을 혁신적으로 바꾸고 있는 인공지능(Artificial Intelligence, AI). AI를 알고, 이해하고 또 활용하고 싶은 이들을 위해 <AAA - All Around AI>에서 AI 기술에 대한 모든 것을 알려드립니다. 1화에서는 인공...](https://raptor-hw.net/xe/files/thumbnails/198/205/241x165.crop.jpg)

![[All Around AI 1편] AI의 시작과 발전 과 [All Around AI 1편] AI의 시작과 발전 과 by 인공지능](https://raptor-hw.net/xe/files/thumbnails/198/205/262x75.crop.jpg)