SRAM은 프로세서의 온 칩 캐시, 마이크로 컨트롤러(마이크로 컴퓨터)의 워크 메모리 등에 표준적으로 쓰이고 있다. 왜 SRAM이 사용되는 가의 가장 큰 이유는 CMOS 로직과 같은 프로세스에서 제조할 수 있는 점이다. DRAM은 제조 프로세스에 캐패시터를 만드는 공정 외 사용시에는 데이터를 정기적으로 다시 쓰는 리프레시라는 다소 특수한 제어를 해야 하지만 SRAM에는 이러한 번거로움도 없다.

DRAM 셀을 SRAM 화한 "1T-SRAM"기술

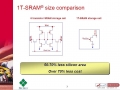

SRAM의 약점은 메모리 반도체 중 기억 밀도가 가장 낮은 점이다. 표준적인 SRAM 메모리 셀은 6개의 트랜지스터를 필요로 한다. DRAM은 1개의 트랜지스터와 1개의 축전기에서 메모리 셀을 구성한다. 단순히 소자 수만으로 비교해도 3배의 차이가 있다.

여기서 DRAM 셀의 제조 프로세스를 CMOS 로직 호환으로 변경하고 리프레시 자동 제어를 추가하거나 주변 회로를 SRAM과 마찬가지로 취급할 수 있도록 변경한 메모리 기술이 1990년대 말에 등장했다. "1T-SRAM" 이라고 불리는 이 기술은 미국 기업 MoSys가 개발했다. 1T-SRAM 기술은 대규모 프로세서의 라스트 레벨 캐시(LLC)과 SoC의 대용량 워크 메모리 등에 채용됐다. "1T-SRAM"의 호칭이 "eDRAM"이라고 불리기도 한다.

본격적인 원 트랜지스터 SRAM 셀의 제안

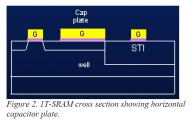

"1T-SRAM" 셀 및 "eDRAM" 셀의 약점은 메모리 셀 면적의 축소가 3분의 1정도에 머무는 것과 리프레시 대기시 소비 전류가 어느 정도 존재하는 것이다. 전자는 평면상 캐패시터가 어느 정도의 면적을 필요로 하기 때문에 일어난다. 캐패시터를 입체화하면 셀 면적을 작게할 수 있지만 프로세스 비용은 CMOS 로직보다 늘어난다. 후자의 리프레시 동작은 기억 노드가 캐패시터이기 때문에 불가피하다.

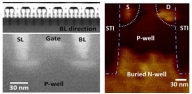

이들 문제를 해결할 목적으로 개발된 것이 본격적인 원 트랜지스터 SRAM 기술 "1-transistor(1T)Bi-SRAM" 이다. 미국의 기술 개발 벤처 Zeno Semiconductor와 미국의 반도체 벤더 Marvell Semiconductor, 미국의 스탠포드 대학(Stanford University)이 공동으로 개발하고 있다. 그리고 Zeno Semiconductor는 스탠포드 대학 출신 연구자가 중심이 되어 설립됐다. 이들 공동 개발 팀은 미국 워싱턴 D.C.에서 개최된 전자 디바이스 기술 국제 학회 IEDM 2015에서 12월 9일에 개발 기술의 개요를 발표했다.(강연 번호 26.7)

MOS FET과 2개의 세로형 바이폴라 조합

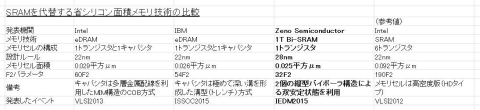

개발중인 기술 "1T Bi-SRAM"은 제조 프로세스에 CMOS 로직과 호환성이 있어 전환 동작 없이 1개의 MOS 트랜지스터보다 약간 큰 실리콘 면적에서 SRAM 셀을 실현한다. 메모리 셀 면적은 6트랜지스터 SRAM 셀의 약 5분의 1이며 MoSys의 "1T-SRAM(eDRAM)" 기술보다 기억 용량당 실리콘 면적이 작아 제조 비용을 낮출 수 있다.

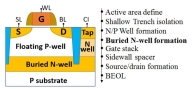

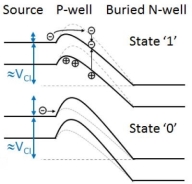

개발한 메모리 셀 구조는 1개의 n채널 MOS FET과 2개의 세로형 바이폴라 트랜지스터를 일체화한 것. 바이폴라는 MOS FET의 n형 소스(또는 드레인)이 이미터, 방출 p형 웰기반, 매입 n형 웰 콜렉터의 3층 구조다. 내장 n형에는 표면의 전극(충전 주입기)를 통해서 전압을 제어한다.

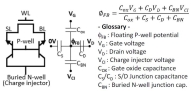

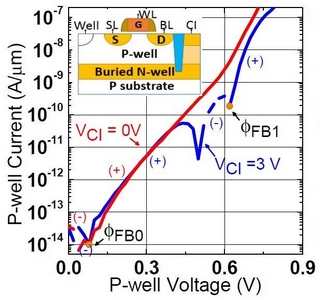

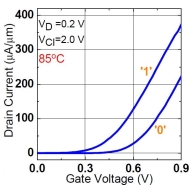

2개의 세로형 바이폴라는 베이스를 공유하고 베이스 부분(p형웰)은 전기적으로는 부유 상태(부유 기준)에 있다. 여기에서 워드 라인(게이트) 비트 라인(드레인) 소스 라인(소스), 충전 주입기(콜렉터)의 전압 값을 적절히 조정하면 부유 베이스에 2개의 불안정한 상태(쌍 안정 상태)를 만들어 낼 수 있다. 하나는 드레인 전류가 높은(논리 값 "높음" 또는 데이터 "1" 에 상당) 상태, 다른 하나는 드레인 전류가 낮은(논리 값 "낮음" 혹은 데이터 "0" 에 상당) 상태다.

쌍안정 상태를 데이터의 "1"과 "0"으로 지정

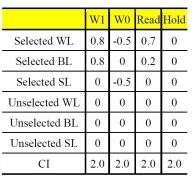

동작의 핵심이 되는 것은 세로형 바이폴라의 콜렉터에 상당하는 포함 n형웰(충전 주입기)의 전압이다. 충전 주입기에 일정한 바이어스 전압을 가함으로써 부유 기반에 쌍안정 상태가 발생하기 때문이다. 이 바이어스 전압의 존재를 전제로 워드 라인과 비트 라인, 소스 라인의 전압을 조정하여 쓰기 동작이나 출력 동작, 대기 동작(데이터 유지)을 실행한다.

고속·고주파 성능 확인은 지금부터

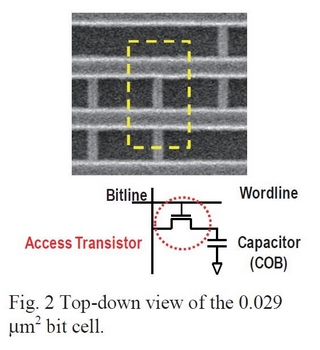

강연에서는 28nm의 CMOS 로직 호환 프로세스로 메모리 셀을 제작한 결과를 보여주고 있었다. "1T Bi-SRAM" 셀의 실리콘 면적은 0.025평방μm으로 상당히 작다. 설계 규칙(F)의 2제곱에 비해서 어느 정도의 크긴지를 나타내는 파라미터는 F2의 32배(32F2)다. 설계 규칙이 짧으면 메모리 셀 면적이 작아지는 것은 당연한 것으로 설계 규칙의 영향을 제거하고 메모리 셀 기술을 비교할 때는 이 파라미터를 사용하는 것이 많다.

이 파라미터를 기존의 대규모 고성능 프로세서 전용 eDRAM 기술과 비교해보면 인텔이 22nm 기술로 개발한 eDRAM의 메모리 셀 면적은 0.029평방μm으로 이것도 꽤 작다. 다만 설계 규칙(F)이 22nm이므로 F2로 환산하면 60배(60F2)로 "1T Bi-SRAM" 셀의 2배 가까운 실리콘 면적이 필요하다.

IBM이 22nm 기술로 개발한 eDRAM 메모리 면적은 0.026평방μm으로 더 작다. 다만 이것도 F2로 환산하면 54배(54F2)로 "1T Bi-SRAM"셀의 32F2에 비하면 상당히 크다. 또 IBM의 eDRAM 셀은 CMOS 로직은 프로세스 기술이 크게 다르다. 실리콘으로 가늘고 깊은 홈을 판 캐패시터를 형성하고 있기 때문이다.

안타깝게도 "1T Bi-SRAM" 셀 배열 구조와 고속·고주파 특성 등은 이번 IEDM에서는 공표되지 않았다. 향후 연구 개발의 진전을 기다리고 싶다.

출처 - http://pc.watch.impress.co.jp/docs/column/semicon/20151217_735749.html

![[All Around AI 1편] AI의 시작과 발전 과정, 미래 전망 우리 삶을 혁신적으로 바꾸고 있는 인공지능(Artificial Intelligence, AI). AI를 알고, 이해하고 또 활용하고 싶은 이들을 위해 <AAA - All Around AI>에서 AI 기술에 대한 모든 것을 알려드립니다. 1화에서는 인공...](https://raptor-hw.net/xe/files/thumbnails/198/205/241x165.crop.jpg)

![[All Around AI 1편] AI의 시작과 발전 과 [All Around AI 1편] AI의 시작과 발전 과 by 인공지능](https://raptor-hw.net/xe/files/thumbnails/198/205/262x75.crop.jpg)