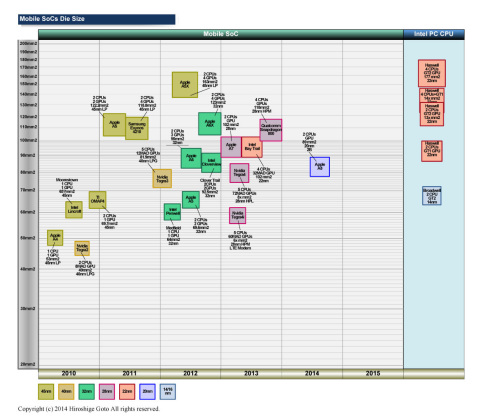

모바일 SoC가 20nm로 이행하는 한편 GPU는 28nm

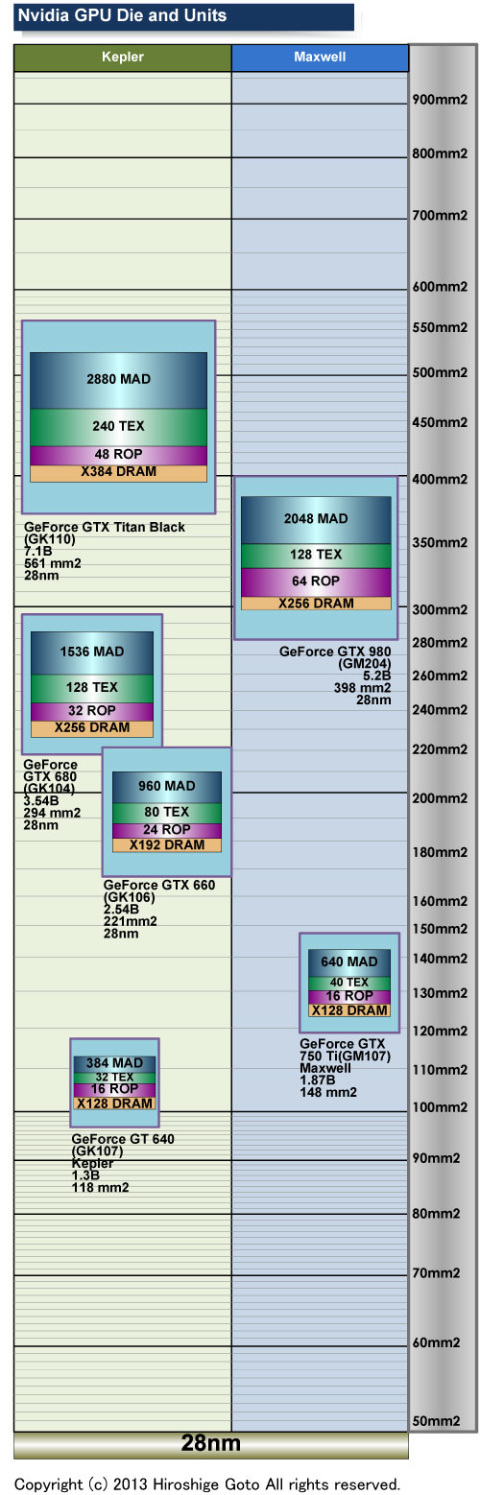

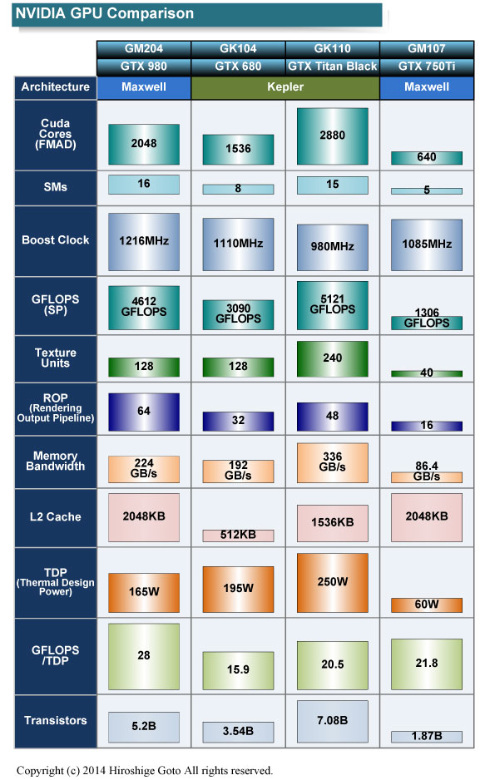

요란하게 등장한 NVIDIA의 고성능 GPU Geforce GTX 980(GM204)이지만 그 제조 공정 기술은 기존대로 28nm 프로세스다. Apple의 iPhone 6/6 Plus의 A8 모바일 SoC(System on a Chip)는 20nm로 이행했는데 이 시기의 NVIDIA GPU는 20nm로 이행하지 않았다. Maxwell GM204는 기존 NVIDIA의 GPU가 채용해 온 TSMC의 "28HP"프로세스 상태다. 그래서 GM204는 400평방mm에 가까운 대형 다이의 GPU다.

예전에는 첨단 프로세스는 가장 먼저 GPU가 채용하고 있었으나 지금은 모바일 SoC가 역전되어 있다. Apple 뿐 만 아니라 Qualcomm도 20nm 칩을 이미 제조하고 있다. 게다가 이들 1위 모바일 SoC는 NVIDIA의 퍼포먼스 GPU와 비교하면 초반 생산 개수가 훨씬 많다. 즉, 개수가 많고 제조가 힘든 모바일 SoC가 새로운 프로세스로 이행하고 개수가 적고 편한 퍼포먼스 GPU가 옛 프로세스에 머물고 있다.

왜 이런 현상이 발생했을까. 그 배경에는 몇 가지 이유가 있다. 물론 Apple의 iPhone 6/6 Plus 때문에 TSMC의 20nm 제조 라인이 압박되어 타사가 라인을 취하기 어렵다는 사정도 있다. 하지만 그것 이상으로 GPU에서는 20nm 프로세스로 이행하는 경제적 이유가 희박하다는 중요한 요인이 있다.

GPU의 경우 20nm프로세스로 이행해도 당장은 트랜지스터당 비용이 떨어지지 않는다. 그것은 웨이퍼를 처리하는 비용이나 새로운 프로세스 개발을 위한 비용이 20nm에서 올랐기 때문이다.

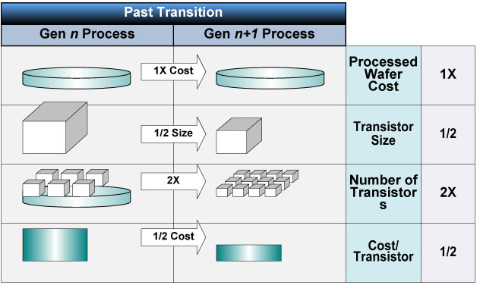

이상적인 스케일링은 프로세스도 웨이퍼 비용을 증가시키지 않고 프로세스 노드를 이행 시키는 것. 그 경우에는 웨이퍼의 비용은 같기 때문에 트랜지스터 사이즈가 1/2로 웨이퍼당 트랜지스터 수는 2배로 하여 트랜지스터당 비용이 2분의 1이 된다. 공짜로 2배 숫자의 트랜지스터가 손에 들어가게 된다.

실제로는 지난 몇 세대에 걸쳐 프로세스도 웨이퍼의 비용은 계속 오르고 있다. 프로세스 공정이 점점 복잡해지고 있기 때문이라는 것. 그래도 CMOS 스케일링의 효과는 웨이퍼당 비용 상승을 넘어 트랜지스터당 비용은 떨어졌다.

프로세스도 웨이퍼의 비용 상승으로 이행의 의미가 퇴색

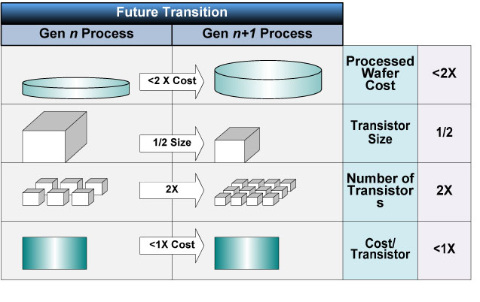

그러나 이제부터 프로세스의 미세화로 웨이퍼당 비용이 급 상승하게 되면 스케일링으로 커버할 수 없다. 만약 1세대의 미세화로 웨이퍼당 비용이 2배까지 늘어난다면 CMOS 계수로 실린 트랜지스터 수가 2배가 되어도 비용 절감 효과가 상쇄되고 만다. 실제로는 거기까지는 올라가지 않지만 GPU에서는 트랜지스터당 비용이 앞선 세대에 비해 크게 떨어지지 않고 있다.

그렇게 되면 이 정도 트랜지스터 수의 GPU 라면 미세화해도 비용이 많이 떨어지지 않아 미세화의 의미가 없다. 그리고 트랜지스터 수를 배증시킨 칩을 만들면 다이당 비용은 지금보다 크게 늘어날 것이다. 트랜지스터 비용이 올라가더라도 이익이 큰 고가의 칩은 어느 정도 맞지만 경제성이 중요한 미들 레인지 아래 칩은 미세화가 맞지 않게 된다.

GPU에서는 현재 비슷한 일이 벌어지기 시작했다. 그래서 GPU는 20nm 프로세스로 이행해도 트랜지스터당 비용은 당장은 별로 내려가지 않는다. 그러면 무리해서 20nm 프로세스로 이행해서 다이 사이즈를 줄이는 것 보다 28nm인 채로 다이를 대형화하여 제조한 것이 경제적으로 유리하게 된다. 적어도 수량이 낮은 시기에 무리를 해서 20nm 다이를 시작할 뜻은 희박하다. 파운드리는 새로운 프로세스의 초기는 비싼 요금 설정을 하고 경쟁이 심해진 성숙 과정은 요금 인하 경향이 있어 구형 프로세스가 유리하다.

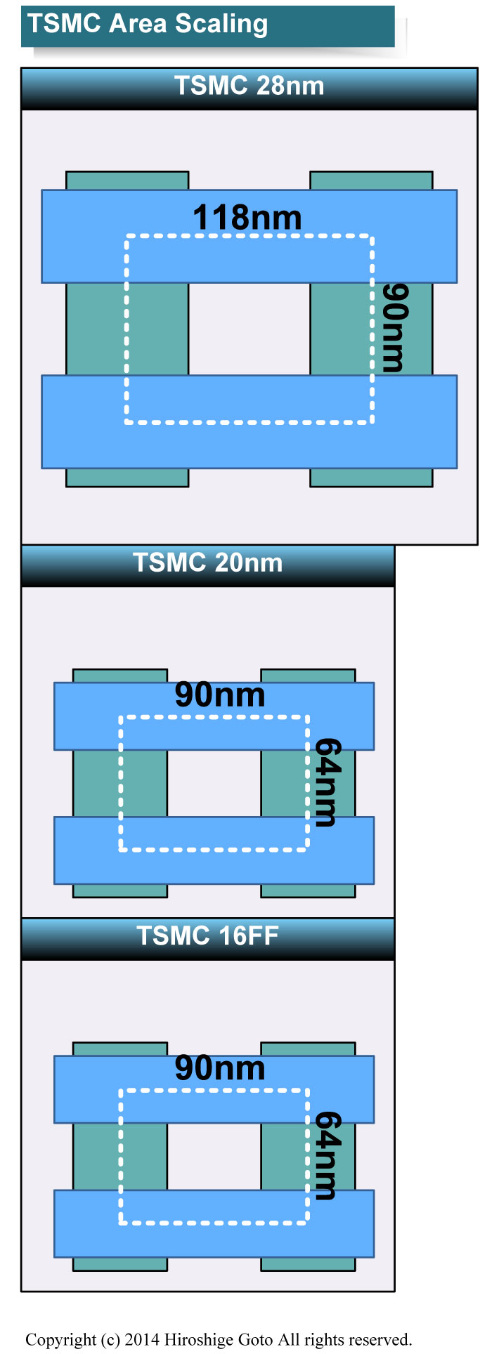

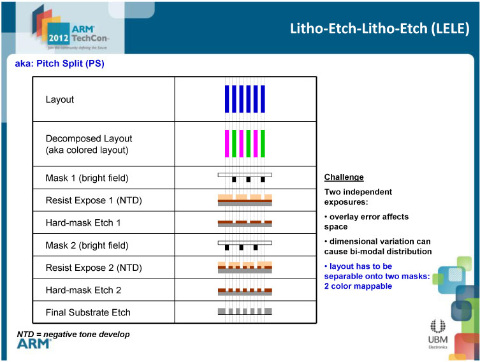

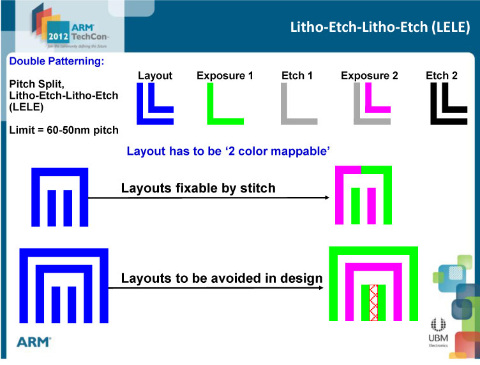

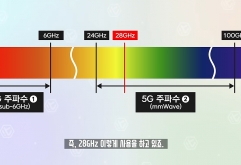

이런 사정은 GPU 뿐 아니라 모바일 SoC에서도 같다고 생각할지도 모른다. 그런데 그렇지 않다. 20nm 공정에서 프로세스도 웨이퍼의 비용이 오르는 주된 요인은 배선층에 "더블 패터닝(Double Patterning)"을 도입하는데 있다. "LELE(Litho-Etch-Litho-Etch)"에서 리소그래피와 부식을 2겹으로 하는 더블 패터닝에 따라 백 엔드 프로세스의 산출량이 떨어지기 때문이다. 그런데 더블 패터닝에 따른 비용 증가의 영향은 칩 종류에 따라 다르다. 이는 배선층의 방법이 다르기 때문이다.

모바일 SoC와 개별 GPU의 다른 사정

GLOBALFOUNDRIES의 Subramani Kengeri(서브라마니・켄게리)는 5월 방일시 다음과 같이 설명하고 있다.

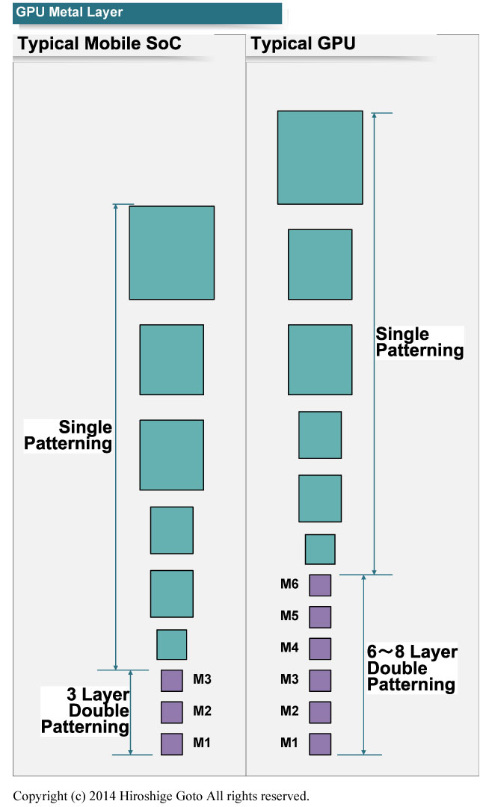

"개별 GPU를 보면 1x의 가장 좁은 메탈 레이어를 사용하는 층은 6층부터 8층이다. 20nm 프로세스에서 이들 1x 층은 더블 패터닝을 써야 한다. 이것에 비해 모바일 컴퓨팅 제품에서는 1x를 사용하는 층은 단 2~3층이다. 더블 패터닝을 쓰는 층의 수는 개별 GPU에 비해 모바일 컴퓨팅이 훨씬 적다. 그래서 비용에 대해 누구와 이야기를 하는지에 따라 크게 차이가 난다"

GLOBALFOUNDRIES는 20nm에서 비용 증대를 들먹이는 것은 GPU라고 지적하고 있다. 사실 이 문제를 가장 강하게 지적하는 곳은 NVIDIA다.

전형적인 모바일 SoC나 CPU는 20nm 공정에서도 더블 패터닝을 필요로 하는 최소 피치는 최하층의 M1/M2/M3의 3층에 있다. 모바일 SoC는 비용을 낮추기 위해 CPU의 저항이 적은 저 지연 배선을 하기 위해 좁은 그라운드에 배선층 수를 한정하고 있기 때문이다. 그래서 20nm 공정의 더블 패터닝에 따라 백 엔드 프로세스의 비용이 높아지고도 3층 뿐이므로 영향은 어느 정도 한정된다.

그런데 개별 GPU에서는 더블 패터닝을 사용해야 메탈 층의 수가 극단적으로 늘어난다. GPU 벤더는 프로세스 옵션이 허락하는 한 최소 피치의 레이어를 높이는 경향이 있기 때문이다. 전형적인 GPU에서는 배선층 중 최하층에서 중층까지의 6층 정도가 최소 피치인 것이 많다. 극단적인 경우 8층을 최소 피치하는 경우가 있다. 따라서 GPU 쪽이 20nm 프로세스의 처리량이 심하고 처리 비용이 대폭 상승하는 것이다.

슬로우 다운한 20nm로의 이행

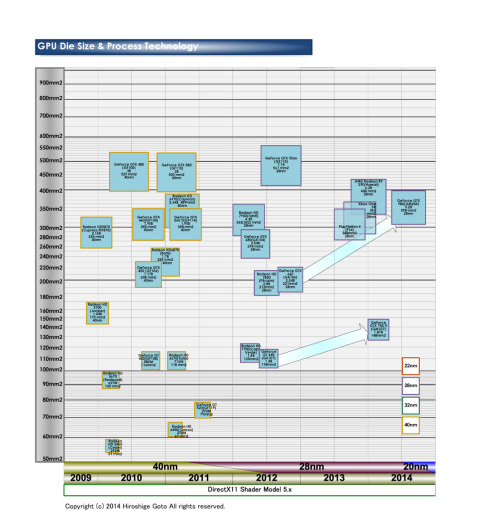

GPU에서는 20nm 프로세스로의 이행이 슬로우 페이스다. 그 결과 GPU는 28nm 프로세스에 3년이나 머물게 되는 아키텍처 확장이 제약되어 있지만 NVIDIA의 경우 원래 Maxwell로 전력 효율을 높일 예정이었는데 28nm 공정에서도 전력을 낮추고 퍼포먼스를 올리는데 성공하고 있다.

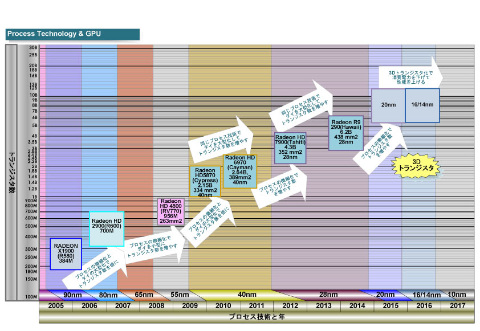

하지만 같은 프로세스에서 다이를 대형화하고 트랜지스터 수를 늘려야 했다. 기존의 프로세스 미세화로 다이 크기를 한정하면서 트랜지스터 수를 늘리겠다는 GPU 진화와는 확실히 다른 길을 걷고 있다. 아래는 AMD의 GPU 프로세스 기술과 아키텍처 확장 흐름으로 28nm 프로세스에서 고생하는 것으로 나타났다.

참고로 이번에 NVIDIA는 TSMC의 28HP 프로세스를 채용했지만 더 높은 퍼포먼스인 "28HPP"(차기 PS4 APU가 이것이라고 본다)과 고밀도"28HPC" 저전력 "28HPM"(모바일 SoC가 많이 채용하고 있다)을 채용하지 않은 이유는 모른다. 28nm 공정으로 간다면 종전 프로세스를 변경하지 않는 것이 모듈의 유용성 면에서 용이하다고 판단했기 때문일지도 모른다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/20140922_667855.html

![[All Around AI 1편] AI의 시작과 발전 과정, 미래 전망 우리 삶을 혁신적으로 바꾸고 있는 인공지능(Artificial Intelligence, AI). AI를 알고, 이해하고 또 활용하고 싶은 이들을 위해 <AAA - All Around AI>에서 AI 기술에 대한 모든 것을 알려드립니다. 1화에서는 인공...](https://raptor-hw.net/xe/files/thumbnails/198/205/241x165.crop.jpg)

![[All Around AI 1편] AI의 시작과 발전 과 [All Around AI 1편] AI의 시작과 발전 과 by 인공지능](https://raptor-hw.net/xe/files/thumbnails/198/205/262x75.crop.jpg)